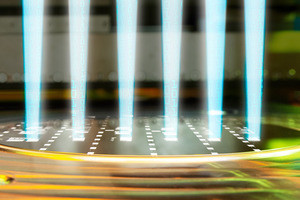

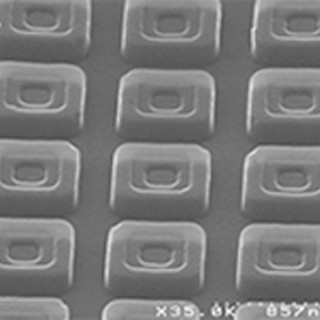

MEMS・半導体デバイス製造向けウェハ接合およびリソグラフィ装置メーカーであるオーストリアEV Group(EVG)は、既存のウェハ接合技術とプロセスおよび接合層材料を利用したDie-to-Wafer(D2W)ハイブリッド一括接合技術において、プロセスフロー全体を通じ2μm以下の配置精度を実証したと発表した。

同成果は、次世代の2.5Dおよび3D半導体パッケージにヘテロ集積化(HI)の適用を加速させるための重要なマイルストーンになるとしている。なお、デモンストレーションで使用した基板は仏CEA-Leti/IRT Nanoelecより提供を受けたという。

今回のD2W一括接合プロセスの結果をハイライトした技術文書は、先般開催されたElectrochemical Society(ECS)PRiME 2020 Conferenceにて発表され、ECSのWebサイトよりダウンロードすることができる。

ヘテロ集積化に必須となるD2W一括接合技術

人工知能、自動運転、拡張/仮想現実、5Gなどといった最先端のアプリケーションでは、高帯域幅で高性能な低消費電力デバイスを低コストで開発・生産することが求められている。

従来の2Dによる半導体のスケーリングが製造コストの問題に直面したことで、半導体製造はヘテロ集積化へと進もうとしている。つまり、1つのデバイスもしくはパッケージ内に、さまざまなサイズ・材質による異なる部品やダイを複数集積することで、次世代デバイスの性能向上を図ろうとしようというのである。3D IC、チップレットやセグメント化された3D SoCといった新タイプのデバイスを低コストで製造するために、機能層や良品ダイのトランスファーを可能とするD2W一括接合はヘテロ集積化に必須なプロセスとなると同社では説明している。

EVGの知的財産・技術開発本部のディレクターを務めるMarkus Wimplinger氏は「EVGはヘテロ集積化への進歩をサポートするため、20年以上にわたり実証済みのソリューションと専門知識を提供してきた。D2W接合もその1つであり、EVGの技術が多くの量産アプリケーションで採用されている。また、EVGは新たに3D/ヘテロ集積化を用いた製品やソリューションを顧客やパートナーに対し、開発基盤を提供することで、必要不可欠とされる機能の強化を図っていく。これらの一環として、新しいD2W一括接合によるアプローチが開発され、今回の研究で、主要なすべての工程を高い配置精度と歩留りで実行可能であることが証明された」と述べている。