米国時間で10月20日~10月29日にかけてオンラインで開催されていた「Linley Processor Conference Fall 2020」の最終日、Armは「Cortex-X1」の詳細を明らかにするとともに、Cortex-A78の派生型として「Cortex-A78C」を発表した。

Cortex-X1とは?

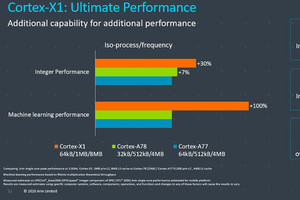

Cortex-X1は5月26日にCortex-A78と共に発表されたCXC(Cortex-X Custom)Programの最初の成果物であり、その概略はこちらでもレポートした通り。また、このCortex-X1をサーバー向けにカスタマイズしたと思われるものがNeoverse V1であるという話はこちらでご紹介したが、そのCortex-X1の中身が従来よりも細かく明らかにされた(Photo01)。

まずフロントエンドで言えば、BTBの容量は5割増え、Fetchは5命令/cycle、Micro-Op Cacheは8 Micro-Op/cycleでそれぞれデコーダに引き渡すようになった。Cortex-A78はFetchが4命令/cycle。Micro-Op Cacheは6 Micro-Op/cycleとなっている。ちなみにBranch Predictorは最大2 Branch/cycleの処理が可能で、これはCortex-X1もCortex-A78も同じようだ。

Dispatchからは8 Micro-Opが同時発行される(Photo03)。ALUは6つ、FPUは4つの実行ユニットが用意される形だ。またDispatchを強化したことに対応して、Out-of-Order Windowsサイズも40%大型化したとされる。ここには載っていないが、恐らくROBなども大型化されていると思われる。加えて言えば、FP/ASIMD側のIQもサイズは倍増しているだろう。

LSU廻りで言えば、構造そのものはCortex-X1(Photo04)とCortex-A78(Photo05)でまったく同じである。Data L1およびL2のBandwidthが倍増とあるのはCortex-A77比の話で、Load/Store Unitそのものの扱うデータ量が16Bytes/cycleから32Bytes/cycleに強化されたものと考えられる。他にもIn-Flight LoadのWindowsサイズを33%増強とか、L2 TLBを66%増強など、データアクセスに向いた対応が行われているのが判る。さらに言えば、L2が最大1MBに強化されたほか、8MBのL3もサポートしているとの話である。

-

Photo04:FPUを倍増させている割にはLoad/Storeユニットがやや貧弱、という気もしなくはない。最大だと512bit分のデータが1cycleで出てくるので、Loadが64Bytes/cycle×2、Storeが64Bytes/cycle×1でもいいような気もするのだが

-

Photo05:こちらはCortex-A78で、性能/エリア比とか性能/消費電力比を意識してか、L1-Dそのものもオプションだし、L3はサポートしていない。Storeは256bit幅である

モバイル向けながらエッジなども想定した「Cortex-A78C」

次がCortex-A78C。こちらはCortex-A78の派生型であり、一応モバイル向けとは言いつつも、どちらかというと据え置き型とか、説明には無かったがIoT Edgeとかにも向いている気がする(Photo06)。

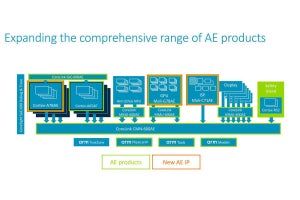

さてまずマルチコア構成。DynamIQを利用したいわゆるbig.LITTLEの構成では、Cortex-A78がbigコアとなり、他にCortex-A55あたりをLITTLEコアとして組み合わせる訳だが、Cortex-A78CはUnified、つまり全コアをCortex-A78Cとし、6ないし8コア構成を可能にするほか、最大で8MBのL3が利用可能となる(Photo07)。

このCorte-A78Cのターゲットは“Big screen Device”という説明であるが、これ(Photo08)を見るとほぼPCの様なノートPCや車載機器などが挙げられている。

-

Photo08:要するにCompute Intensiveなデバイス向けという話で、それこそEdge IoT Gatewayとかに向いてる気がする。AWS Greengrassなど、丁度手頃なApplicationではないだろうか?

“Big screen”で筆者が連想したのはMicrosoftのPixelSense(“Surface Table”と言った方が判りやすそうだ)であるが、あながち間違っていないのかもしれない。

もう1つ、Cortex-A78Cで追加されたものがSecurity廻りである。ROP(Return-Oriented Progamming)とかJOB(Jump-Oriented Programming)は、プログラムの不正侵入で非常に良く利用される技法で、あらかじめ不正なコードをメモリ中にロードしたうえで、ReturnなりJumpなりの飛び先を書き換えて不正コードに制御を移す、という手法である。これに対応するものとしてArm v8.3-aではPointer Authentication Code(PAC)という機能が追加された。これは飛び先アドレスの一部をシステム内で登録済のPACに置き換えることで、仮に飛び先アドレスを書き換えられるとPACが無くなってしまうため、不正な飛び先と判断して実行を中断する仕組みである。これそのものはCortex-A78にも搭載されているのだが、Cortex-A78CではArm v8.6-A(Matterhornで実装されるもの)で用意されるEnhanced Pointer Authentication Code(EPAC)を利用可能になる、とされる(Photo09)。

-

Photo09:このEnhanced Pointer Authentication CodeはちょっとDeveloper.arm.comを探ってみたのだが、詳細が見つからなかった(URLは見つかったのだが、Page not found扱い)。現時点(2020年11月2日)ではまだ詳細が公開されていないのかもしれない

現時点ではArmはまだこのCortex-A78Cを正式には発表していない。これは11月5日から始まるArm DevSummitの会場でのお披露目になるのだろうか? 期待して待ってみたいところである。