理研の研究者がArmの「SVE」を評価

COOL Chips 21のプロセサのセッションで、Armの「Scalable Vector Extension(SVE)」の電力性能の分析と題する論文が発表された。

筆者がこの論文に興味を持ったのは、この論文の著者が、「Odajima」、「Kodama」、「Sato」の3氏となっていたからである。佐藤三久氏は、理化学研究所(理研) 計算科学研究センター(京コンピュータが設置されており、ポスト「京」コンピュータの開発を担当する)のアーキテクチャ開発チームのリーダーであり、児玉祐悦氏は、筑波大の教授から理研に移られ、現在は、アーキテクチャ開発チームのナンバー2のシニアサイエンティストである。そしてCOOL Chips 21で論文を発表した小田嶋哲哉氏はアーキテクチャ開発チームの特別研究員である。

-

この研究の背景。幅の広いSIMD演算器を搭載して性能を上げるのが一般的であるが、チップ面積が大きくなるし、消費電力も増える。どうするのが良いかを探るのがこの研究の目的 (このレポートのすべての図は小田嶋氏の発表スライドの抜粋である)

SVEの構成の違いによる性能と電力を評価

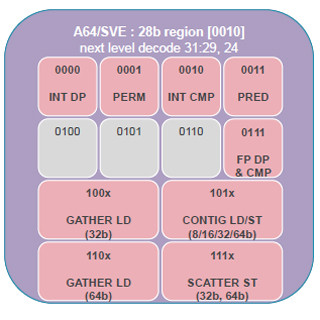

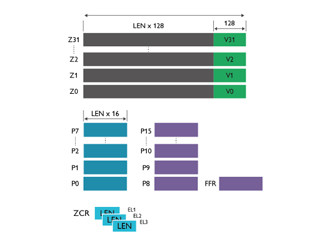

ArmのSVEアーキテクチャでは、SIMDのベクトルレジスタの長さは128bitの倍数で、 128bit~2048bitの範囲で選ぶことができる。ただし、SVEアーキテクチャではベクトルレジスタの長さとは無関係(Vector Length Agnostic)に同一の命令で任意の長さのベクトルを処理できるようになっている。

当然、ハードウェア的にはベクトルレジスタの長さの単位で繰り返し処理を行っているのであるが、命令的にはそれは見えないようになっている。この特徴を利用して、この研究では異なるハードウェア的な構成を作って、その性能と電力を評価している。

-

128bit×N(最大2048bit)のベクタ長をサポートする。SVEではハードウェアのベクトル長と関係なくプログラムの変更無しに任意の長さのベクトルを処理できる。なお、富士通のPost-Kプロセサのベクトルレジスタは512bitとなっている

この評価には「gem5」という汎用のプロセサシミュレータと「McPAT」という消費電力を計算するフレームワークを使った。この研究では512bit長のレジスタを使う「LEN=4」、1024bit長のレジスタを使う「LEN=8」と、論理的にはLEN=8であるがLEN=4とハードウェア量を同程度とするため、1サイクルのSIMD演算は512bitとし、1024bitのSIMD命令の発行には2サイクルを必要とする「LEN=8 half」という3つ構成を評価している。

Gem5とMcPATを使うシミュレータ環境は、次の図のようになっている。gem5で命令レベルのシミュレーションを行い、FPUの動作回数やキャッシュのヒット率などの統計情報とハードウェア構成の情報を出力し、McPATに送る。McPATはプロセスルールやITRSのプロセス情報から各動作の1回あたりの消費エネルギーを計算し、gem5からの動作回数の情報と合わせて消費電力を計算して出力する。また、McPATはSIMD演算器の面積なども出力する。

-

シミュレーションにはgem5とMcPATを使う。gem5はプログラムの実行に伴うFPUの動作回数やキャッシュのヒット/ミス回数などを出力する。McPATはプロセス情報から1回の動作に伴う消費エネルギーを求め、gem5からの動作回数を掛けて消費電力を出力する

この研究ではクロックは2GHz、L1Dキャッシュは32KB、L2キャッシュは2MBで、浮動小数点パイプラインは2本、ロードストアパイプラインは、各1本と想定している。また、半導体プロセスは45nmを想定している。

Post-Kコンピュータには、恐らく7nmプロセスが使われると思われ、45nmという古いプロセスを想定しているこの研究のチップ面積や消費電力はかなりずれているものと思われる。しかし、この論文で比較している3種の構成についての消費電力や性能の相対値は、大きく外れていないと期待される。

3種類の構成のチップ面積を比較

LEN=8はLEN=4と比べると演算器の幅が2倍になるので、FPUとレジスタを合わせたチップ面積は1.95とほぼ倍増する。一方、LEN=8 halfは1024bitのデータを扱うのでベクトルレジスタは倍増するが、演算器の個数はLEN=4と同じである。また、リネームレジスタを16個に減らしていることもあり、面積の増加は10%に留まる。

そして、性能、電力の評価ではN=512、TIME_STEP=1のN-Body計算とN=25600、TIME=STEP=10のStream Triadの2つのプログラムを使っている。

-

この論文ではLEN=4、LEN=8とLEN=8 halfと呼ぶ3つの構成を評価している。LEN=8とLEN=8 halfで違いのある重要項目を楕円で囲んでいる。LEN=8 halfはピーク演算性能が半分、ベクトルレジスタの数も半分になっているが、チップ面積はLEN=8が1.95であるのに対して、LEN=8 halfは1.10と小さい

次の図の右側の棒グラフは、3種の構成のプロセサのチップ面積を比較したものである。なお、前の図ではFPUとレジスタの面積だけを比較しているが、次の図ではL2キャッシュとOthersも加えたプロセサ全体の面積を比較している。

棒グラフの色分けは、下から順に、L2キャッシュ、Othersで、この部分の面積は3種の構成とも同じである。その上がFPUsとFP Registersである。LEN=4の構成を1.0とすると、LEN=8ではFPUの演算器、レジスタともに幅が2倍となりプロセサの面積は38%増加する。

LEN=8 halfは1024bitのSIMD演算を2サイクルかけて計算する方式で、演算器の面積はLEN=4の場合と比べて微増である。アーキテクチャレジスタは、当然、1024bitのものが32本必要であり、LEN=4のケースと比べて倍増する。しかし、リネームレジスタは、LEN=4では512bitのレジスタを64本持っているのに対して、LEN=8 halfでは1024bitのレジスタが16本となっている。ピークの演算スループットはほぼ同じであり、LEN=8 halfの方がオペランドの粒度が大きい分、端でのロスが増えるので、リネームレジスタはLEN=4の場合と同等か、それよりも多く必要と思われるのであるが、なぜか、16本に減らされている。