|

|

図1 東芝技監の明島周三氏 (出所:半導体パッケージ展Webサイト) |

「FOWLP(Fan Out Wafer Level Package)」は半導体実装業界にとって昨年来最大の話題になっている。2017年1月18日~20日に東京ビックサイトで開催された第18回 半導体・センサ パッケージング技術展の併催セミナーで、東芝ストレージ&デバイスソリューション社研究開発センター技監の明島周三氏が「世の中を騒がしているFOWLPってこれからどうなるか?」と題して講演したので、ここに要約して紹介したいと思う。

FOWLPとは、どのようなパッケージ技術なのか?

でもその前に、あまりなじみのない方のために、簡単にFOWLPについて説明しておこう。

FOWLPは、もともと2005年に独Infineon Technologiesが開発した技術で、当初から将来有望なパッケージング技術として一部では注目されてはいたが、製造歩留まりが低いこともあって、なかなか普及しなかった。しかし、2016年にAppleがTSMCが開発した独自FOWLP「InFO(Integrated Fan Out)」をiPhone 7/7Plusのアプリケ―ションプロセッサの実装に全面採用したことで、一気に業界全体の注目を集め、普及に拍車がかかった実装技術である。

従来、Appleのアプリケーションプロセッサの受託生産はTSMCとSamsung Electronicsが受注を分け合っていたが、iPhone 7/7Plusに関しては、FOWLP技術の開発が遅れたSamsungを尻目に、TSMCが全量受注を勝ち取ったと言われている。

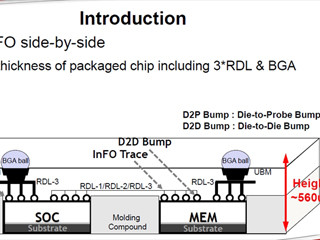

FOWLPの概略図を図1に示す。半導体チップの端子から配線を引き出す再配線層をウェハプロセスを用いて形成することで、パッケージ基板をやめて、ワイヤもバンプもなく、製造費用を安く、厚みを薄くできる。再配線層は薄膜のため配線長を短くできるので、電気信号の伝送速度を高速化できる。従来のWLCSPがパッケージ面積と半導体チップ面積が同じであるのに対して、FOWLPはチップの外側まで端子を広げるためパッケージ面積が半導体チップより大きく、多ピン対応が可能で、微細化によるチップの小型化にも対応できる。製造コストが高いTSV (シリコン貫通ビア)を用いず複数の半導体チップ(たとえばMPUとDRAM)を積層して小型化を図るSiP(System in Package)のプラットフォームとなることが期待されている。

再配線層を形成するため、パッケージ工程に前工程のウェハプロセスが持ち込まれることで前工程と後工程の垣根がはずされ、ファウンドリがフルターンキーで受注するようになった。アセンブリ受託企業やアセンブリ基板メーカーは、死活問題になりかねない。TSMCに敗れたSamsungも再びiPhone向けビジネスを獲得しようと追い上げに必死だ。あっという間にビジネスを失う企業がある一方で、FOWLP特需で新たなビジネスチャンスをつかむ半導体製造装置・材料メーカーも続々登場している。