16FF+による次期GPU"Pascal"が登場予定

2015年は20nmプロセスを放棄して28nmに戻りつつ、Keplerよりも効率は良い(ただし倍精度浮動小数点演算は切り捨てた)Maxwellアーキテクチャを投入してなんとかラインナップを維持したNVIDIAだが、やっとTSMCの16FF+が使えることになった。

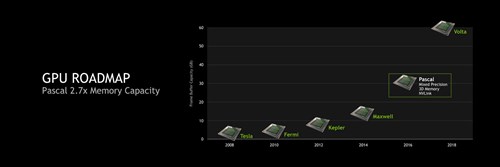

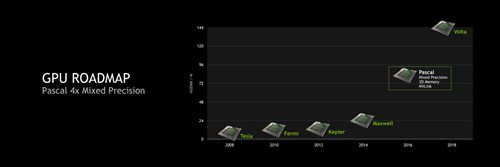

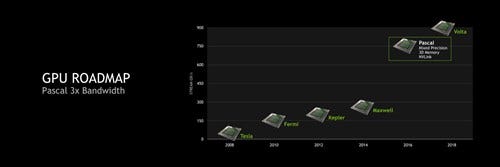

2015年4月に開催されたGTC 2015で次期GPU"Pascal"の概略は紹介されており(Photo32~36)、いまの時点でそれほど新情報はない。とりあえずハイエンド向けコア(GP100?)の構成は、いまのGM200に匹敵するものになるだろう。ただそのGP100、規模としてどの程度になるのかを占うのは難しい。

|

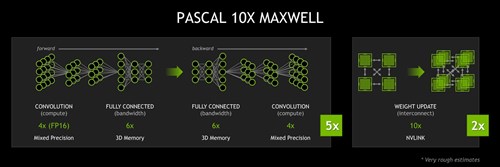

Photo34:Mixed Precision、つまり単精度と半精度(16bit Float)を混載する演算では最大4倍の性能になる。これはそもそもMaxwellがFP16の演算器を持っていないのが問題 |

|

Photo35:MaxwellベースだとGeForce Titan Xが7Gbps/384bit幅で336GB/sec、対してPascal世代ではHBM2×4で、1TB/secになるからほぼ3倍である |

|

Photo36:先のPhoto34でいえば、Convolutionの計算でMixed Precisionの演算になるところがそのまま4倍になる。トータルとして、Deep Learningの処理はPascalがMaxell比で10倍高速という試算である |

実はNVIDIAはこのPacalというかGP100をすでにチラ見せしている。2015年9月に開催された2015 Taiwan GTCのDeep Learningにおける講演のスライドの中に、明らかにGP100ボードと思しきものが示されている(Photo37)。

|

Photo37:これはNVIDIA TaiwanがアップロードしたYouTubeビデオの2分47秒あたりから示されている |

ちょっとスライドが荒すぎて、ここからダイサイズなどを推定するのは困難(というか、一応やってみたのだが無理だった)であるが、総トランジスタ数は170億個とされており、これはGM200の2倍以上である。

28nm→16nmだとエリアサイズはおおむね52%ほどにしか縮小されない(これは16FF/16FFが配線層は20nmと同じことに起因する)関係で、トランジスタ数が倍以上ということは、ダイサイズは恐らく600平方mmを軽く超えることになる。

ちなみにCUDA Core数は4,096基だそうである。GM200と比較するとちょっと不思議かもしれないが、PascalはFP64、つまり倍精度小数点演算もサポートする模様で、そうなるとFP64を切り捨てて高密度化したMaxwellと比較するのではなく、FP64をサポートするKepler世代のGK100と比較するのが妥当だろう。GK100が2880 CUDA Coreなので、まぁ倍にはなっていないが、概ね良い数字なのではないかと思う。

ただGP100は、恒例のごとくTeslaとGeForce Titan向けに留まり、メインストリーム向けとしてはGP104あたりが投入されるだろう。恐らくCUDA Core数は3,000台で、かつFP64のサポートを省き、その分ダイサイズを小型化する方向になる。

ハイエンドはHBM2が搭載され、ミドルレンジはGDDR5Xあたりになるだろうが、GP104が両方のI/Fを持つのか、それともGP104はHBM2のみで、GP106あたりがGDDR5Xになるのか、あるいはGP104以下は全部GDDR5Xなのか、などについてはいまのところ情報がない。

製品というかGP100のお披露目そのものは、2016年4月に予定されているGTC 2016になると思われる。極端なことをいえば、まだ出荷出来ない状態だとしても、お披露目はここしかありえないだろう。問題はこれらがいつ市場に投入されるかである。

一説によれば、16FF+についてもNVIDIAは相変わらずプロセスで苦しんでいるらしい。動作周波数が想定どおり上がらないことに加え、巨大なダイサイズのお陰でYieldもまだ十分に高いとはいえないとか。

実際TSMCは、多くのSoCを16FF+で流し始めているが、ほとんどはMobile向けの小さなダイ(Chipworksによれば、AppleのA9でも104.5平方mmとかだそうだ)であり、サーバー向けにHiSiliconが試作した32coreのCortex-A57を搭載したチップも、ダイサイズは200平方mm未満(このチップはI/Oを28nmで製造したMCM構成なので、16FFで製造するダイはCPU+共有キャッシュ+Interconnectのみということで、それほど大きくならなかった)でしかない。これだけ大きなチップはTSMCとしても初体験に近く、当然Yieldの上がり方はかなり緩やかになるだろうと思われる。

というわけで、このあたりの問題をいつ解決して出荷できるかは、中の人ですら分からないという状態になっている。とりあえずまだ台湾のボードパートナーに広くサンプルが廻っているという状態でもないので、少なくとも4月のGTCのタイミングでGP100/GP104カードが広く販売されるという可能性はかなり低い。早くて6月のCOMPUTEXでサンプルが各社から展示されるというあたりではないかと予想される。