8月にレポートしたSkylakeのレビューで、筆者はセンチュリーマイクロのDDR4-2133 DIMMのプロトタイプを利用したという話をちょっとご紹介した。

その後同社は定格でDDR4-2400 DIMMを発売して話題になったが、さらにDDR4について話題がでた。それが「JEDEC RAW CARD Version B1 GERBER」である。ただこれも言葉だけ先行していて中身の説明がないので、今回はこのあたりをもう少し深く掘り下げて解説したい。

そもそもガーバーとは何か

ガーバー(GERBER)を普通に検索するとナイフメーカーにたどりついてしまうのだが、電子回路の世界におけるGERBERとは設計図(もっと正確に言えば設計図を格納するファイルフォーマット)のことで、もともとはGerber System Corp.という会社が、プリント基板(PCB:Printed Circuit Board)向けのCAD用に開発したものである。

Gerber System Corpは1998年にBarco ETS(現在のUcamco)に買収されてしまっており、会社そのものは残っていないのだが、同社が残したファイルフォーマットはデファクトスタンダードとして現在も使われており、この結果としてガーバーと言えば設計図ファイルを指すのが普通だ。

さて、これがDIMMにどう関係してくるかだが、メモリチップそのものはメモリベンダが開発するが、それを適当に基板に載せて配線しても、必ずしもメモリ本来の性能が出るとは限らない。そこでJEDECでは、このDIMMの基板についても「標準的なガーバー」と呼ばれるものを策定している。この標準的なガーバーなるものがいわゆる「JEDEC RAW CARD」である。

このJEDEC RAW CARDのガーバーファイルは、JEDECのメンバー企業が設計を行い、検証後にこれをメンバー会員に公開する形をとっている。ちょっと古い話になるが日本ではかつてメルコ(現Buffalo)が、この標準ガーバー作りに熱心であった。2000年にはこんなリリースを出しているし、その後はSO-DIMMやMicroDIMMなどの標準ガーバー策定に引き続き関与している。

ただ、DDR4に関してはまだそもそも出たばかりの規格であり、またサーバー向けが先行した関係でSO-DIMMなどはこれからということになっていた。そのため、現時点では目立った成果は出てきていない。

さて話を戻すが、DDR4に関しては、IntelのX99プラットフォーム(というかDDR4利用のXeon)がまず立ち上がったので、すでに標準ガーバーはリリースされている。Unbuffered DIMMに関してはこちらで公開されており、

| 構成 | ECC | Revision | 公開日 |

|---|---|---|---|

| 1rank x8 planer | No | A0 | 2014年8月20日 |

| 2rank x8 planer | No | B0 | 2014年2月24日 |

| 2rank x8 planer | Yes | D0 | 2014年2月24日 |

| 2rank x8 planer | Yes | E0 | 2015年2月26日 |

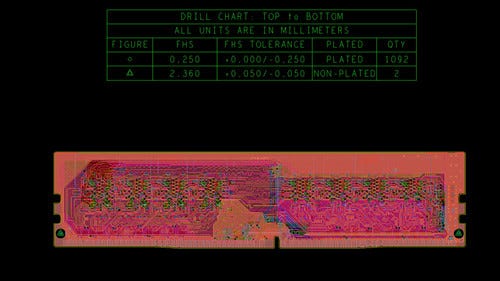

という4種類のガーバーが現在確認できる。このうち一番上のA0は1rank、つまり片面実装のモジュールであり、両面実装のものがB0/D0/E0である。ただし、D0/E0はRegistered DIMMなので、最もよく使われている両面実装のUnbuffered DIMMはRevision B0として規定されている(Photo01)。

|

Photo01:Revision B0のガーバーの配線(TOP/3層/4層/6層/Bottom)を表示させた状態。表示にはcadenceが無償配布しているAllegro Free Physical Viewerを利用した。これを使うと誰でも表示は出来る(編集するにはPCB CADが必要) |

ちなみにこの標準ガーバーは、あくまで「この設計図通りの配線で、指定された材質や構造にしたがって作れば、想定どおりのタイミングでDRAMがアクセスできる」というものだから、必ずこの標準ガーバーを使わなければいけない。というものではない。

ちょっと古い話だが、例えばCorsairは以前からオーバークロックメモリに独自基板を使っており、GND層を広く拡張し、そこにヒートシンクを着けることで、チップだけでなく基板からの放熱も可能としている。同社のDomoinatorシリーズのDDR4 DIMMもそんな構造を踏襲している。

当然これは標準ガーバーのままでは無理なので、独自に設計を行っている訳だが、別にこれでもタイミングとか負荷が満足されるのであれば構わない。ただ、そもそもこうした独自DIMMの設計にはそれなりの時間が掛かるうえに、それが正しく機能する(単にDIMM単体で機能するのみならず、プラットフォームとして機能することも求められる)かどうかの検証に結構な手間がかかるので、よほど自信があるか、何かしら新機能(Corsairの例で言えば放熱機能)を追加したいとでもいうのでない限り、標準ガーバーを使うのが得策である。

そんな訳で現在市場に出ているDDR4-2133 Unbuffer DIMMのほとんどはRevision A0もしくはRevision B0で作られているが、実際のマーケットを見ると、片面実装タイプはほとんどなく、両面実装の8GBモジュールがメインとなるので、そういう意味ではほぼすべてRevision B0といってもいいだろう。

Intelが新ガーバーの策定を主張?

ところがこれに強烈な介入をしたメーカーがあった。ほかでもないIntelである。背景はよく分からないのだが、X99では問題のなかったRevision B0のDDR4-2133 Unbuffered DIMMが、どうもSkylake(というかZ100)で使うにはいろいろと問題があったらしい。

実際初期のプロトタイプ(筆者が評価したES品の2つほど前あたりのRevision)では、動かないだの立ち上がらないだの、動いたけどすぐ落ちるだのといった問題があったと聞く。

一体どのあたりが原因だったのかはさっぱり分からないのだが、この解決策としてIntelはDDR4-2400までの動作に対応した「Revision B1」の早期策定をJEDECのJC4-45.3(JEDECでのDRAM Moduleを策定するJC-45のなかで、さらにUnbuffered DIMM Modulesを策定する分科会)で強硬に主張したらしい(このあたりは全部伝聞である。もちろん公のドキュメントには一切出てこない)。

この結果として、2015年5月に策定されたのが、今回話題になっているRevision B1のSpecificationと、そのガーバーである。細かい説明は後でするとして、結果から言うとSkylakeのDDR4コントローラが、予想ほど信号駆動能力が足りず、これが理由で条件によってはまともにDDR4のアクセスができなくなる、という現象が起きていたように見える。

このあたりは完全に筆者の推測なので、本当かどうかまでは分からないが、結果としてこうした問題の解決のためにB1ガーバーが予定よりかなり前倒しで出てきたと判断するのが正しいかもしれない。

あるいは、2016年早々に登場といわれるBroadwell-E(チップセットはX99のまま)がDDR4-2400に対応していることや、"Skylake Refresh"こと"Kabylake"もどうやらDDR4-2400対応になることがほぼ確定したようなので、この辺りも含め早めにDDR4-2400への筋道をつけておきたかった、ということも副次的要因としては考えられよう。