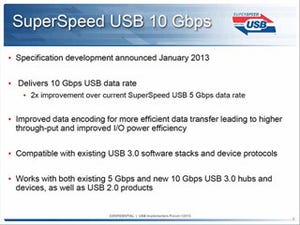

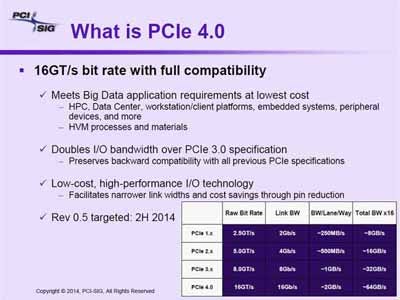

PCIe Gen4

最後がPCIe Gen4である(Photo10)。基本的には「On Trackだ」(Yanes氏)という話であるが、昨年の見通しだとRevision 0.5が2014年Q1、0.9が2015年Q1だったから、予想通り1Q~2Qほど遅れていることになる。

|

Photo10:スケジュール以外、内容はほとんど前回と同じ |

このBase Specification、「2.0→3.0の時は、単に速度を変えるだけでなく、Encode Schemeを変更したり、新しくEqualizingを入れたりとずいぶん変更があったから大変苦労したが、今回はスピードを変えるだけだからそう難しくない」(Yanes氏)としている。

ただその割に、Revision 0.5がいまだにDevelopmentの状況にあるあたり、決して容易とはいえない。このPCIe Gen4、ターゲットとしてはFinFETを使ったプロセス(TSMCの16nmかGlobalFoundries/Samsungの14nm)の可能性が高い、としつつもまだ確定してはいないという返事であった。これはBase SpecificationとProcessの両方が難航していて、すり合わせできる状況にないからと考えるのが一番妥当だろう。

この先のスケジュールであるが、「0.5は近いうちにReleaseしたいと考えている」とした上で、「一般論として、まず仕様を公開して、Reviewの期間が1カ月、その後Clean-upに1カ月、さらにそのあと60日の検討期間が設けられる」としている。ただRevision 0.7とか0.9になると、実際にそれを基にテストチップを製造し、それの検証を行うといった作業が必要になることを考えると、実際には半年以上が掛かるかもしれない」(Neshati氏)という話であった。

実際、PCIe 3.0の時も、Revision 0.7で一度テストチップを試作したところ問題が判明、Revision 0.71を新たに追加し、これでの検証を経てRevision 0.9に移行した事を考えると、それなりに時間が掛かると考えるのは妥当である。そうした事を考えると、問題なく順調に進んだとしてもRevision 0.7がReleaseされるのは2015年Q2以降、Revision 0.9が2015年末か2016年Q1、Revision 1.0になるのは2016年2Hというあたりだろう。また、もし何かしら問題が出るとここからさらに半年位後まで送りになっても不思議ではないところだ。

ちなみにテストチップに関しては、PCIe 4.0ではT-Coilといったアナログ部品をSoC上に構築する必要があり、これの手順なども反映させる必要があるので期間が長く掛かるとの事だった。

ただここまで時間が掛かると、ターゲットアプリケーションは何か? という問題が当然出てくる。Gen4のターゲットアプリケーションとしてYanes氏は「Big Dataの時代になって当然トラフィックが増えているから、そうした用途に倍の帯域のGen4が適している」と説明したが、ご存じの通りネットワークトラフィックはもっと速いペースで増加しているし、そもそも2016年とか2017年まで待っていられない状況である。

これに関してNeshati氏に「そもそもそんなに待てない顧客が、10G/40G/100GのEthernetとか、独自のバスなどをつかってのSolutionを既に提供し始めている状況では、Gen4がReleaseされても対応アプリケーションはそう多くならないのでは?」と振ったところ、「確かにその考え方自身には同意するが、われわれは製品ではなくあくまでもI/FのSpecificationを提供する立場であり、こちらを使うのか、それとも独自規格を使うのかはユーザー(機器ベンダー)が判断することだ」とした上で、「これまでもそうだったが、一部のベンダーはDraft段階の仕様を元に製品を出すこともあるから、ひょっとするともっと早くGen4相当の製品が市場にでる可能性はある」と回答した。加えて、「Gen4のメリットは単に帯域を増やすだけでなく、例えば同じ帯域であればGen3の半分のピン数で済むから、実装面積を増やしたい場合にも役に立つ」とした。

またGen4の設計目標として、Gen3と同じレーン数で、同程度の消費電力に抑える(つまり帯域が倍増しても消費電力が変わらない)事を挙げており、もし帯域が同じで良いのであれば、消費電力を下げることもGen4では可能になると説明してくれた。

しかし、問題はそうしたニーズは決して多くないということ。また、特にNetwork Processorのマーケットでは、これまでは40G/100GのEthernetをPCIeで繋ぐという形で実装されていたが、最近は40GのEthernet MACをSoCに統合しているケースが少なくなく、今後は100GのEthernet MACを統合する製品も増えてくると予想される。そうなると、Gen4を使うマーケットそのものが小さくなってゆく。この点を問いただしたところ、Neshati氏は図1の様な図を描きながら、「確かにGen4のマーケットは小さくなると思うが、その分ASPは高くなるから、マーケットが小さくなる分を補える」という見解だった。

もうひとつ気になるのが距離の話。以前も紹介したが、Gen3ではServer Backplane向けに20inch程度の配線の両端にコネクタが装着されるというケースをカバーしていた。これに対しGen4では10~12inchの配線の片側にコネクタが装着される(もう片方はSoCのピンに直接接続される)というケースのみを想定しており、これを超えるような場合にはRepeaterが必要になることになる。

さて、ここで問題になるのがSATA Expressだ。SATA ExpressはPCIeのレーンをケーブルでドライブまで引き回す事になる。SATA-IOは現在のところPCIe Gen2/Gen3をターゲットとしているが、もしGen4が公開されたらこれにも対応することを表明している。その場合ケーブルの長さがどう考えても短すぎる(SATA Experssのケーブルも、長いものは60~70cmある)のだが、これに関しては特にSATA-IOと話し合ったりはしていないということ。

恐らくRevision 0.9が出てくる様になるまでは、明確な動きはないように見える。まぁ幸い(というのもアレだが)、今のところSATA ExperssはGen2 x2構成が殆どで、Gen3 x1/x2構成はまず見かけないから、Gen4の対応を考えるまでの時間は十分にあるということかもしれないが。