Q:それは判ります。ただ20nmに関しては、例えばスケジュールをTSMCが2カ月前倒しにしたという話が出ていて、今年中に少なくともRisk Productionは始まる。そして、14nmというかTSMCだと16nmですが、こちらも2014年末にはRisk Productionは始まりそうです。ということは、2015年位にはVolume Productionになる。で、Xilinxは常に"Cutting Edge Process"を使うという事を話されてますが、ということは2015年の最初の16nmのVehicleにはXilinxが入ってるのかな? と私は考えているのですが。

Rogan:当然我々はそういう流れで動いています。ただ今回は、28nm世代で、日本だけではなくWorld WideでXilinxが有利という事をお客様に認めていただいている。Design Winをトラッキングしているのでそれが判ります。で、今回はパラダイム変更に集中しているので、何かしら次の話題が必要です、と。で、20nmに集中しましょう、となった時に、実は我々は20nmで結構進んでいる。先にTest Vehicle出して、先にSiliconも見てて、結構Designは進んでいるんです。

神保:2013年1月の終わりにAnnounceさせていただいた20nm製品に関するStoryは3つありまして、2013年3月のタイミングで20nm製品に対応したToolがAvailableになる。で、同6月までにTape Outします。で、年内に最初のSiliconがAvailableになる。このStoryは今も変わっていません。ちゃんと最初のMilestone、ToolのEarly Accessに関しては、日本のお客さんも含めてやっていただいおります。

Q:もう少しすると本国で決算発表のConference Call(同社の決算発表は4月24日。実際にインタビューが行われたのは、それよりも少し前の4月10日)がありますが。その時には何かしらこう期待してよろしいと考えてよろしいですか? それとも決算発表だけ?

Rogan:多分、決算発表だけだと思います。

神保:もうXilinxとしては、20nmには技術的なRiskはほとんど無いと判断していていますので1月の段階で、「年内まででこうやって進めていけますよ」って言えたんだと思います。コンサバな会社なんですが、あのくらいはっきり言えたんです。もう20nmに関しては、個人的にはDone Dealなのかなと思っています。

Q:ただ、まぁその次の話が全然見えて来てないですよね? 次のプロセスは結構タイトなスケジュールになっているはずなので。

Rogan:Xilinxはどうかなあ、多分色々な面でリーダーシップを見せていると思いますんで、(20nm Processの次の世代で)Xilinxが大外れになるか、というと多分そうはならないと思います。

Q:つまり20nmの次の世代では、基本的にFPGAベンダはIntelかTSMCのFoundryを使って作られる訳ですけれど、その世代やその次の世代でも要するに「負けないよと」という宣言をしていると考えて宜しいですか? 大雑把に言うと、Intelが今年、14nmのHigh Speed Logic用のプロセスをアナウンスされると思うのでSoC向けは翌年、つまり2014年中にアナウンスされると見られます。すると量産はその翌年、つまり2015年になると思うのですが、その位のTermではXilinxも当然のように何かしらが用意できてると考えてよろしいんでしょうか。

Rogan:少なくても、我々は遅くならない。あと考えなければいけないのは、Intelが自社向け製品のProcessと、Foundry向けのProcessを同じタイミングでやれるかどうか、ですね。やはり自社製品向けが優先になるんじゃないかと思うんですね。あと、FinFETに関しては、非常に面白いテクノロシーだと思いますけれども、まだ量産する為には色々必要あるんじゃないか、と。

Q:まあ今の所Intelだけですからねえ。

Rogan:やはりFinFETをやる場合、いろんな新しいノウハウとか、いろんな予想してない所が、出るんじゃないかなと思うんですけどね。別にFinFETが良いとか悪いとかそういうことではなくて、そんなに単純な話じゃない、というのが我々からのメッセージですね。

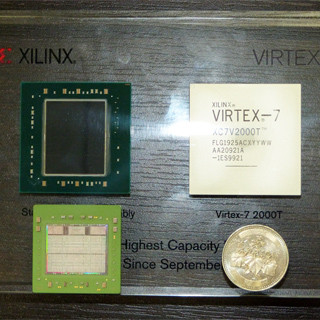

Q:では最後の話を。やはりIntelをFoundryにしているところで、22nmに関してはAcronixとTabulaがそれぞれ出しています。で、Tabulaが特に100Gに特化したFPGAのソリューションを出されている。彼らは100GのWiredに特化していて、もう他の事は一切知らない。で、その100GのSolutionは、XilinxがVirtex-7で出している100GのSolutionと見事にぶつかっているんですが、Samさんから見てTabulaさんはどう思われます?

Rogan:Tabulaは色々なDesign WinのPress Releaseは出されているのですが、売り上げの話を余り聞いたことがありませんので、なんとも(笑)。ただ、TabulaのSolutionは、回路書いて、実行して、再コンフィギュアして、書いて、実行して、再コンフィギュアして、ということをずっと回してる感じですよね。

まあシリコンは別にただな訳じゃないですけど、でも一時期はすごい高かった(からそうした必然性があった)。ところが今は、シリコン回路と規模とかを考える上で、本当にそういう面倒くさい事やる必要あるかどうかが疑問なんですよ。物としては、実行に間に合うように回路書き直しできればいいんです。が、設計するのはとっても大変だと思いますよ。

Q:なるほど。

Rogan:例えばPartial Reconfigurationをやるとき、データのポインタが沢山必要あるんですよね。ある1つのファブリックを書き直す際に、そこにつながってる全部のものが関係してくる。ですので、どうやって他に影響しないようにコントロールするのか、とか。なんというか、Reconfigurationが問題を起こさないようにするための準備のオーバーヘッドが結構大きいんですね。そうした部分に設計のエネルギーを割くのはどうか? と。

少なくとも売り上げでは余り聞いた事無いですし、本流のアプリケーションもあまり聞いた事無いので。Technologyとしては面白と思うんですけどね。

Q:つまりSamさんから見るとまだcompeteはしてないと。

Rogan:competeはしてないですね。我々のメインcompetitorはASICだと思ってるんですよ。Alteraはあともう少し(でキャッチアップできる)。

今、XilinxはDesign Pipelineをすごく細かくトラッキングしてるんですよ。そのDesign Pipelineは、1から5まであって、4から5に切り替えるとWinできるのかな、と。実は6、7があってそれは物流とかそういう部分です。で、1のところを少し見ると、ここはFPGAが向いている。で、2~4がキーの所で、これが全部5になる時に、他社を完全に逆転できるなと思ってるんですよ。もし我々のDesign Pielineの精度が正しいのであれば、ですが。まぁ時間は掛かるけど、FPGAのサイクルは随分長いですし。だから、我々の本当のcompetitorはASICなんです。

Q:面白いですね。ちなみにいつぐらいに、その2~4が5になって逆転できるんでしょう?

Rogan:そこは我々、実は幾つかのすごいBig Winを獲得したんで、その立ち上がり次第なんです(笑)。Near future I thinkですよ、正直言いまして。

ということで

やや漫談めいたインタビューになったことが、実を言うとこれで7割位。残りの3割はさらに脱線しており、記事からは省かせていただいた。当然ながら、ニュースとしてそれほど新しい話題があるわけではないが、Zynqがメインストリーム製品になっているとか、相変わらず主要なCompetitorはASICであるとかの見方はちょっと新しいものだった。

以前もちょっと書いたが、Sam Rogan社長着任前のザイリンクスは10年の間に社長が9人という、ほぼ1年ごとに切り替わる落ち着きの無い状況だったのが、この5年間は同氏がずっと社長を勤めている、珍しく「安定した」状況である。今年後半には20nm世代に関する詳細ももう少し明らかになると思われるわけで、そのあたりをとりあえず楽しみに待っておくのが良いのだろう。