Q:ちょっと話が飛んで恐縮ですが、色々なベンダが、そろそろOpticalに移行しないとまずい、と取り組みを始めてます。で、例えばAlteraなどはもうそうした取り組みを公にしましたが、一部のベンダはチップからのI/FにOpticalを持ち込み始めたりしてます。昨今の動向をみていると、向こう5年位は電気ベースのバスですが、その先はOpticalに移行といった話をしています。

多分その流れの端っこなんですが、残念ながらシリコンは余り光りません(笑)ので、王道を行ってる光の方達と戦えるといった、そんな大それた事を言うつもりは今の所無いんですが、うまく行った暁には、どっか丁度いいサイズのと言うか、要するに距離ですね。そういった規模の物があればそこに食い込んで行きたいな、と。

Q:それは例えばSoC内部のInterconnectを全部Opticalにするとか?

そう、SoCとかSiPであるとか、あるいはそのモジュールとか、そうしたあたりをターゲットにしたいな、と。こうした部分では、大きな送受信モジュールを実装するのは絶対無理だと思いますので。そうすると、もしかしたら座席が残ってると言いますか(笑)、狙える所があったりしないかなぁ、なんていう。ただ現状として言うと、「光る」というだけで嬉しかったのですが。

一応光に関しては、電圧の変調で光の方の波長が少しシフトするとか、そうしたデータも取れてます。本当のPrimitiviな所での光での通信ですね、そういう実験までは一応やってますので、まあ、あながち無理ではないかな? という風に期待できると思ってます。

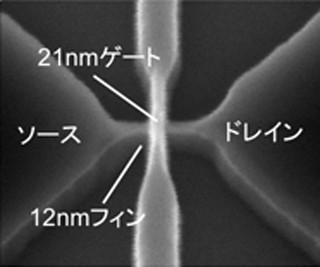

Q:先程、材料の話とmore thanという話がありましたが、シリコンで光らせようと思った場合に、100面だと光らない訳ですよね?で、111面だと面方位が変わるので光るかなっという話が上がってきたりしている訳ですが、そうすると面方位まで意識してFin型構造を作ろうという方に踏み込んでいるのですか?

|

あ、それは実はたまたまなのですが。FinFETを開発した段階では、20年前ですから光らせる方は全然考えて無かったのですが、実はFinを作ってこちら側に出力するという構造をイメージすると、実は面方位がぴったり合うんですね。たまたまだったんですけれど(笑)。ですので、今後もこれで行くのか? と言われたら「知りません」としか言いようが無い(笑)んですが、要するに光らせてみて置いてみたFinの向きと、今まで使ってるというか、Finで一番電気的にGainが出そうな向きが同じなので、同じ面方位でもってやれそうだ、と。ですので、もし本当に使うんであれば、一番Gainがありそうだな、というイメージです。

Q:話が元に戻りますが、今後はTechnology Boosterが無いとすると、2020年以降、つまり量子コンピュータが出てくるまでの間と言うのは、非CMOS系の、例えばIII-V族などの材料を使った有機トランジスタと言いますか、あちらの方に行くんでしょうか?

有機トランジスタなどの研究は1つ盛んになると思います。ただ、現在のCMOSがカバーしているエリアと、有機トランジスタがカバーするであろうエリアは、たぶん違うマーケットです。もちろんそれぞれが大きくなってくれるのが一番嬉しいとは思いますが、基本的には違うマーケットだと思ってます。で、私自身としては、そのCMOS系というか現在カバーしているエリアの中で、ごく低電圧のデバイスの方が多分まだ抜けているという印象を持ってます。

また手前味噌で恐縮なんですが、しかもまだ製品というか、実際実現できるような話では無いのですが、学会発表させていただいてるものとして、Deep Subthreshold処理やTunnel Leakがあります。現在はこちらの系統の方を一生懸命やってまして。この先10年はFinで持たせるとして、その次の10年は電圧と消費電力を下げる事が、CMOSを持たせるために必要な技術になるのかなぁ、というつもりでやらせて頂いてます。

Q:現場と言いますか、半導体の製造現場の方や、営業部でもそうですが、とにかく今、低消費電力のデバイスを寄こせという話になっていまして、むしろそちらの方の需要と言うか、研究加速してくれって話が出てくるんじゃないかなって気がするんですが。

ええ、そう思います。現在電圧を下げられない理由は、まずVtのバラつきの問題。その次の根本的な問題が、Subthreshold Slopeに60mV/decadeという理論限界(*5)が存在してしまっている事ですね。最初のバラつきに関して言うと、今現在の理屈ではFinみたいなやつでノードを下げて、なおかつWを増やす、そんな形で片付ける方向です。

(*5):従来のFETで信号をOn/Offする際には、電流を一桁増減させる際のGate電圧変化(Subthreshold Slope)が60mVを下回ることができないという理論限界が存在する

Q:あとは、Independentで電圧を制御して、バイアス効果を少し期待するとか?

その辺は、もし回路屋さんが許して下さるなら、我々デバイス屋としては、とてもありがたいので。もう、すぐにでもやってくださいとお願いしたいところです。多分あまり受け入れてもらえないですが。なので次の課題として言うと、やっぱりSubthresholdを立てる。それによって電圧を下げて、なんとか0.5V以下、0.4~0.3Vに持って行けるデバイスを作るというのが、10年位のスパンで見た時にFinの次のターゲットになるのかな、と私は考えております。

Q:例えば0.3Vが実現するとして、今問題になっているのは、電圧を下げると電流が増える方向に行ってしまっているので、これを何とかしたい、ということだと思うのですが。

ええ。ですので、すごい荒っぽい計算なんですが、例えばSubthresholdのSlopeを20mVか30mV立ててやってVtを0.3Vまで落とすと、多分OFFの方は現在と同じレベルを保てて、かつ電流の方は(Slopeを立てて)稼ぐ事が出来るようになります。すると電圧が下がった分だけ、電圧の2乗で効いてきます。もし今が1Vでこれを0.3Vにすると、電圧が1/3ですからラフに言えば消費電力を一桁落とせるという絵が描けないことも無いかな、という(笑)。