IDF初日、午後からは、米Intelの上席副社長であるSean Maloney氏の基調講演が行われた。タイトルは「Intel Architecture Innovates and Integrates」で、サーバやデスクトップなどのビジネス向けのPC展開の方向性を示すものだ。

ところが、本来、この基調講演は、Pat Gelsinger氏が担当していたDigital Enterprese事業部のものだったのである。IDF開催前の予定では、ここでPat Gelsinger氏が講演を行う予定であり、一部の案内にもGelsinger氏の名前が挙がっていた。しかし、IDF開催直前に組織変更が行われ、Gelsinger氏は、Intelを退社、それを急遽、Maloney氏が担当したというわけだ。関係者の話によれば、内容もシナリオも、Gelsinger氏が予定していたもの、そのままだという。

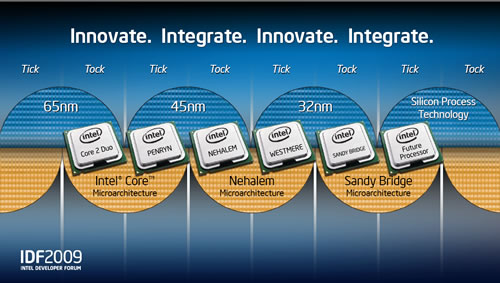

最初に示されたのは、Intelの「Tick Tock」パターンだ。これは、プロセッサのマイクロアーキテクチャ改良とプロセス変更を交互に行うもので、Core 2以後のプロセッサは、このパターンを採用している。本来、講演を行うはずだったGelsinger副社長は、386プロセッサの開発チームに所属していたこともあり、このパターンを特に好んで話していた。現在は、Nehalemマイクロアーキテクチャが登場したところで、次は、プロセスが32nmへ移行する予定で、同じNehalrmアーキテクチャを採用するWestmereが登場する。

|

Tick Tockパターンによるプロセッサ開発。現在は、Nehalemが登場したところで、次は、これを32nmへ移行する。さらにその次には、新しいSandybridgeマイクロアーキテクチャが登場する予定 |

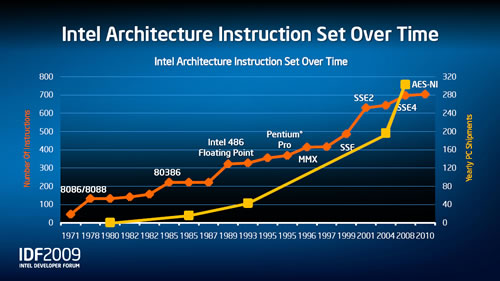

次に示されたのは、プロセッサの命令数のグラフだ。次世代となるWestmereは、マイクロアーキテクチャは、Nehalemと同じだが、AES(Advanced Encryption Standard)暗号の処理を高速化するAES-NI(AES New Instrunction)命令が追加される。AESは、DESに代わる米国の標準暗号化方式であり、たとえば、無線LANの暗号化などに利用されている。AES-NIは、AES暗号の暗号化、解読の処理の一部をSIMD演算機構を使って高速化する。Intelによれば、3倍以上の高速化が可能だという。インターネットやセキュリティなどのため、暗号が使われる場面は増えてきており、AES-NIは、こうしたプログラムを高速化することができる。

グラフには、重ねて、PCの年間出荷台数のグラフが示され、命令数が増え、多くの処理が高速化することで、PCはさまざまな場面に使われていき、出荷台数を増やしていることが示された。現在のインテルアーキテクチャのベースになったのは、386であり、Gelsinger氏には、思い入れがあったので、このような説明になったのだろうが、どうも代役のMalony氏はしっくりこない感じである。

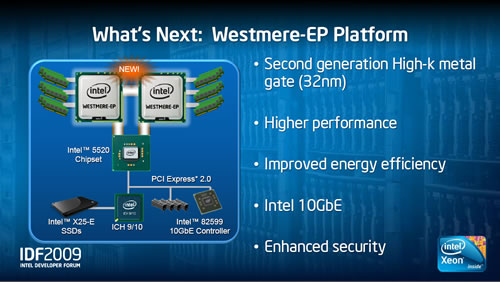

次世代のWestmereを使ったプラットフォームの特徴として、高いパフォーマンス、エネルギー効率の向上、10Gbitイーサネット、セキュリティの強化という特徴が挙げられた。プロセッサは、新しい32nmプロセスで製造され、プロセッサのダイサイズが縮小、また、リーク電流なども少なくなる。