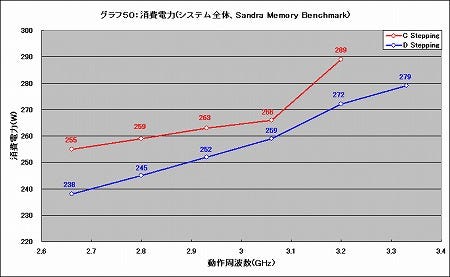

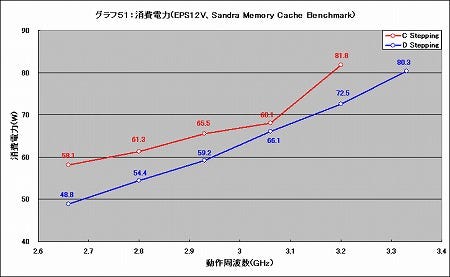

最後にMemory Access時の消費電力をグラフ50・51に示す。グラフ47とグラフ50を比較すると、2.66GHzでは9~12Wと比較的それほどギャップがないのに、3.20GHzだと25~27Wとかなり増えており、L3キャッシュの分を抜いても最大で18~20W近く消費電力が増える計算になる。一方、EPS12Vの方で例えばグラフ49と51を比較すると、こちらもやはり最大で20W強となる。要するにグラフ50の増分は全部CPUによるものというわけだ。

このあたり、以前の考察には若干間違いがある事になる。つまり、

・EPS 12V系からCoreとUnCoreの両方が供給される

・SandraのArithmetic IntではL3やMemoryがフル稼働することはないので、10W未満の数字となるが、これをフル稼働すると30W近い増加となる。

ということだ。グラフ43で、ALU/SSE 4.2をフル稼働させると90Wちょい、ここにL3/Memoryもフル稼働とするとプラス30Wだから、120Wオーバーとなり、TDP枠の130Wまでもうちょいという計算になる。待機時には異様に消費電力が下がるためにそうとは思えないが、見かけ程にはTDPの枠にヘッドルームは無いということであろう。

さて話を戻すと、ここまでの結果をまとめるとC-Steppingには若干問題があるように思える。具体的に言えば、C-Steppingで利用していたトランジスタは3GHz程度まではおとなしく動くが、その先はややVcoreを上げないとちゃんと動いてくれない様に感じられる。これをすると、動作周波数がそもそも上がる上に電圧も上がるから、消費電力は急激に増えることになる。このあたりを改善したのがD-Steppingで、電圧を上げなくても動作するようにトランジスタの性能改善を図り、これの副次的効果としてより低い動作周波数においても省電力化が実現できたというあたりだろうか?