Geneseo

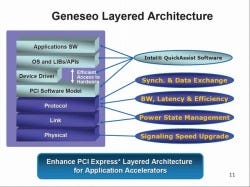

次にそのGeneseoの発表を見てみたいと思う。Geneseoは要するにPCI ExpressをベースとしたInterconnectで専用Acceleratorを接続するものだが、その際にどうプログラミングするか、が問題である。それとは別に、FPGAベースのアクセラレータをFSBに接続するFSB-FPGA AcceleratorをサポートするIntel QuickAssist Technologyが前回のIDFで発表されたが、GeneseoもまたこのQuickAssistを使ってサポートされることがまず明らかになっている(Photo03)。GeneseoとQuickAssistの役割分担を示したのがPhoto04である。PCI Software ModelとかDevice Driver、及びその上位に関してはQuickAssistの領分であり、Geneseoはその下を担う事になる。

|

|

|

Photo03:ある意味QuickAssistはハードウェアを抽象化しており、それがGeneseoなのかFSB-FPGA Acceleratorなのかは無関係である。これにより、結果として(原理的には)AMDのTorrenzaまでQuickAssistまでカバーできることになる。ただ実際には色々面倒な話があるので、直ぐに実現するとは思えないが。 |

Photo04:この図がこうなるとはちょっと予想外だったのは事実。 |

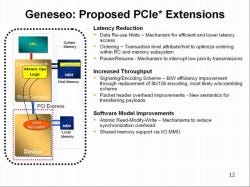

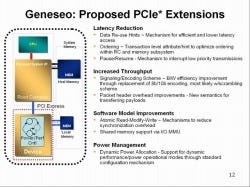

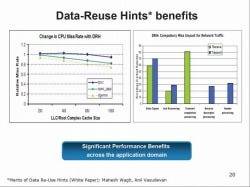

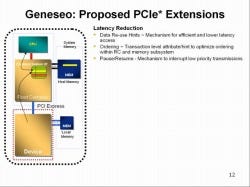

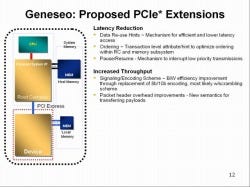

さてそのGeneseoであるが、先ほどのプレゼンテーションと同様の項目が並ぶ。まずLatency Reductionの3項目(Photo05)、ついでIncreased Throughput(Photo06)、Software Model Improvementと続き(Photo07)、最後にPower Managementに続く(Photo08)。各々の機構の詳細はまだ説明がないが、各項目をインプリメントした場合の効果について今回紹介があった。まずData-Reuse Hintsを使うことでの効果(Photo09)だが、TPC-C/SPECjAppServer/DGEMMの各ベンチマークで、Root ComplexにCacheを搭載することで最大30%近くMiss Rateを減らせるとか、Networkの処理において最大80%オーバーヘッドが削減できるといった数字が示された。

|

|

|

Photo05:この図でははっきりと、Root ComplexがLocal Cacheを持つことが見て取れる。転送速度もさることながら、Latency削減を考える上でやはりメモリアクセスがそろそろボトルネックとなる領域に達してしまった、ということだろう。 |

Photo06:この図からもIncreased ThroughputそのものはGen3のBase Specificationの範疇と判る。 |

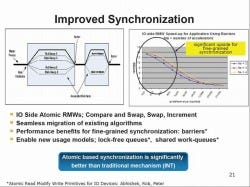

次のSynchronization(Photo10)はAtomic Read-Modify-Writeの部分である。Acceleratorを複数個(2~4個)接続した状態で、Atomic Read-Modify-Writeを使った場合と使わない場合で、どれだけ性能が向上するかを比較した結果がグラフであるが、短時間のLockであれば14%近い性能向上が図れていることが判る。

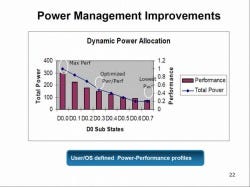

最後がPower Managementである。具体的にどんな構成を取っているか、ということは判らないが、Max PerfとLowest Pwrを比較すると性能は4分の1まで落ちている反面、消費電力も330→70と2割程に減少しており、効果的に省電力機構が稼動している事が判る。