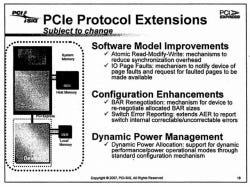

ソフトウェアに関しても、いくらかの拡張が行われた(Photo02)。まずはAtomic Read-Modify-Writeのサポート。要するにクリティカルセクションを提供するものだ。これはRoot ComplexとDeviceの両方で提供される。これもIOVに向けた機能と考えれば良いだろう。ちょっと意外なのが次のI/O Page Faultのサポート。要するにDMA BufferがIn Pageで無くてもI/OをStartできるというものだ。

次のConfiguration Enhancementsも、基本的にはIOV関連の対応と思われる。まずBAR Renegotiationは、BAR(Base Address Registers)を再マップする機能だが、これはIOVにおけるFunctional Resetあたりで便利なものとなろう。つまり、ある仮想OSがDevice Resetを掛けた場合などに使われるのではないかと思う。またSwitch Error Reportingは、AER(Advanced Error Reporting)を拡張するとある。こちらは具体的な項目がまだ未公開なので何とも言えないが。

最後のDynamic Power Managementは、消費電力削減である。具体的に言えば、不要な場合に帯域を落すというもので、例えばx16→x8→x4→x1といったバス幅削減と、転送速度の削減(8GT/s→5GT/s→2.5GT/s)の両方をカバーするものになる、という話だった。ただ具体的な話はまだ不明で、例えばx0がありうるか(*1)とか、2.5GT/s未満のスピードがあるか、といったあたりは現状不明である。

このProtocol ExtentionとGeneseoの関係については、はっきりと「これがGeneseoだ」とYanes氏が言っており、つまりこれはIntel/IBMとの協議の中で決まった機能ということになる。このPCI Expres Protocol Extensions、あくまでもGen3世代で導入するとしており、前倒ししてGen2世代に導入する予定は無い、との返事だった。

(*1) 普通に考えればx0、つまり転送中止はありえないのだが、PCI Expressの場合Reset信号が別に用意されるので、これを使えば一度x0に落としてから復帰することは不可能ではない。ただReset信号に複数の意味を持たせることになるので、本当にやるかどうかはちょっと不明だ。