ムーアの法則の終焉で始まる新たな法則

Moore's Law(ムーアの法則)の終焉が心配されているが、ムーアの法則の終焉は、ムーアの法則以外のすべてのその他の方法の発展の始まりになるかも知れないとSterling教授は言う。

これまではハードウェアの実装の制約でノイマンアーキテクチャが使われてきたが、その制約が取り払われる可能性がある。ALUやFPUの利用率の最適化は間違いだった可能性があるし、計算のロジックとメモリを分離したことは、当時のテクノロジに依存したもので、現在ではVon Neumannボトルネックと言われるようになってきた。

また、順次の命令イシューは自然な並列性の利用を妨げると言われているし、メモリのシーケンシャルコンシステンシー(メモリアクセス動作をシーケンシャルに実行した場合と同じ結果になるようにすること)はメモリアクセスの並列実行を制約する、また、キャッシュコヒーレンス機構を必要としている。

そして、レジスタは独立したローカルなメモリ空間を作り、ロード/ストアによるアクセスが必要になる。論理的にレジスタ空間は独立であり、時によってはレジスタが不足することが起こるほか、レジスタの長さは一定で、データが短ければ無駄が生じるし、レジスタより長いデータは格納できない。

このように、当たり前と考えられてきたアーキテクチャは、みんな間違いであったかも知れない可能性がでてくる。

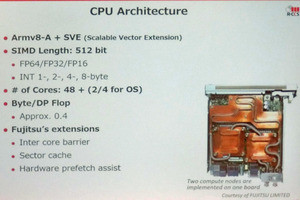

Sterling教授らが、Caltechで行った「Continuous Computing Architecture(CCA)」というアーキテクチャは、Fontonと呼ぶ基本ブロック(128Mopsの演算器と1KBのメモリを持つ)のアレイを搭載したチップを使って高密度のロジックを実現しようとするアプローチである。

次の図の上側の表では、チップは1万1000個のFontonを集積し、ソケットには4チップ、ボードには372ソケット、モジュールには4ボード、ラックには168ボードを収容する。そして、1008モジュール(24ラック)のシステムを作るという実装イメージが書かれている。

下の表は、各実装レベルの演算性能などをまとめたもので、上記のシステムのピーク演算性能は8.41ExaOps、1.05ExaFlopsで67.3TBのアクティブメモリと1.61PBのDRAMメモリを持つ。

すべてのFontonは同じものであるので、Fontonからの出力は近傍のFontonに送って処理を行うと言うようにすれば、信号の遅延時間が短縮でき、信号伝送のバンド幅も非常に大きくできるという。

-

Continuous Computing ArchitectureではFontonと呼ぶ演算器とメモリからなる基本ブロックのアレイに演算のグラフを貼り付けて短い配線で計算を行いチップを小さくし、性能を高める

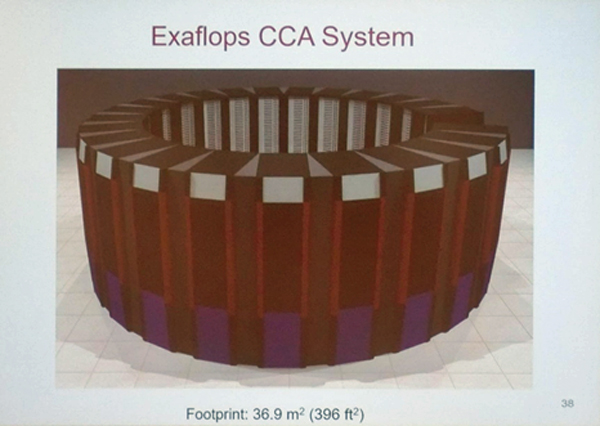

次の図は、24本のラックをリング状に並べたExaFlopsの性能を持つCCAシステムのイメージである。計算上は、36.9m2の床面積に設置できる。

Exaの先にあるZetta、そしてYotta

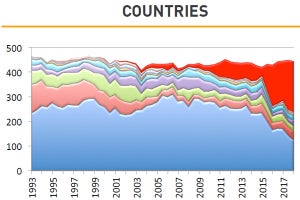

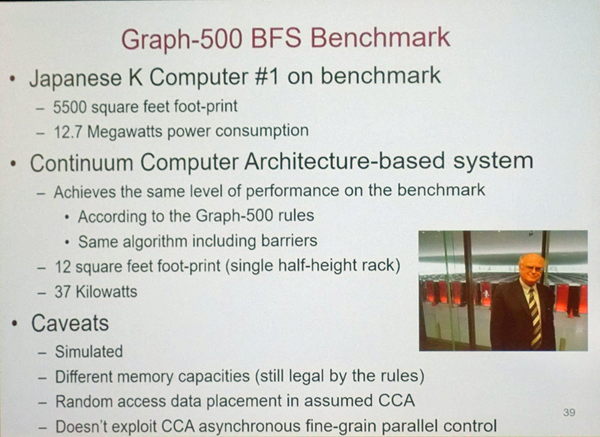

Graph500は、Summitなどの新たなTop500上位のシステムでの計測が無く、日本の京コンピュータが引き続き1位を守った。しかし、このシステムは設置面積が5500平方フィートで、消費電力が12.7MWである。

前の図に示したCCAアーキテクチャのマシンなら、同程度の性能を半分の高さのラック1本で実現できる。設置面積は12平方フィートで、消費電力は37kWで済む。この結果はシミュレーションでは確認しているが、実際にCCAマシンを作ってはいない。

-

Graph500はSummitなどでの測定がなく、京コンピュータが1位を守った。このシステムは設置面積が5500平方フィートで、消費電力が12.7MWである。CCAアーキテクチャのマシンなら、高さ半分のラック1本で同程度の性能が得られ、消費電力は37kWで済む

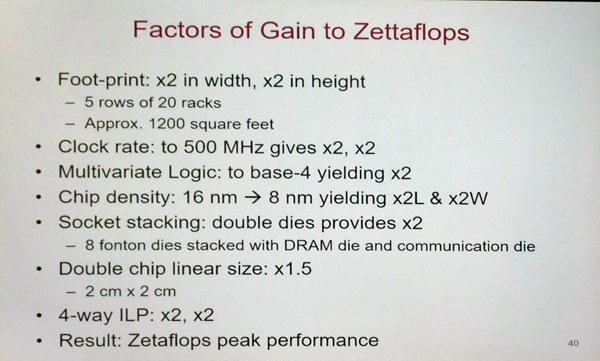

ZettaFlopsに向けて、どのようにして性能を上げて行くかであるが、まず、設置面積を4倍にして20ラック×5列とする。その次に、クロックを500MHzに倍増する。さらに、4値ロジックを使って演算性能を倍増する。

チップのプロセスを16nmから8nmにシュリンクし、4倍の素子を集積する。チップをスタッキングして素子の密度を2倍に上げ、チップサイズを大きくして1.5倍の素子を集積し、4Way ILPで性能を2倍に引き上げる。これらすべてが目標通り実現できれば、性能を384倍に引き上げることができるという。筆者の数え間違いかも知れないが、ちょっと計算が合わないが、ピーク演算性能をZettaFlopsにできるとする。

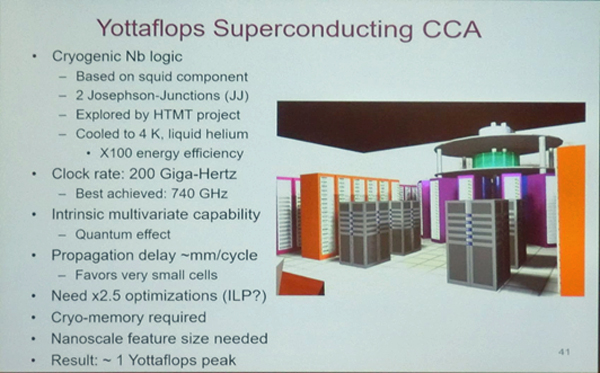

そして、YottaFlopsに達するには、ロジック素子を超電導素子にして、クロックを200GHzに引き上げる。クロック1サイクルはmmサイズの配線遅延と同程度になるので、非常に小さいセルが必要になる。

クロックアップだけでは不足で、さらに2.5倍の性能アップが必要になる。また、ごく低温で動作するメモリも必要であるが、これらが実現すれば、YottaFlopsのピーク演算性能にも手が届く。

これはSterling先生の個人的見解で、講演の中でも過去の発言の間違いを認めて訂正を行ったりしているように、すべてが正しいとは限らない。しかし、HPC業界のビジョナリーの1人であるSterling先生のジョークを交えた講演は人気があり、ISCの大トリの基調講演として15年続いている。

そして、この講演の結論のムーアの法則の終焉は、その他すべての方法の始まりかも知れないという見方は、非常に勇気づけられるものであった。