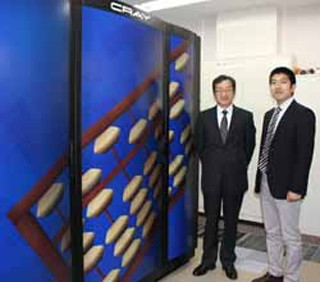

Cray-1システム

Cray-1は、計算セクション、メモリセクション、I/Oセクションからなっている。計算セクションは命令を解釈して、演算を行う部分で、前述のECL回路で作られている。

メモリセクションは、1語64bitで容量は、最大1M語である。これまでの計算機ではコアメモリなどが使われていたが、Cray-1のメモリはフェアチャイルドの1KbitのECLメモリLSIを使っている。サイクルタイムは50nsで、コアメモリと比べると1桁以上高速のメモリである。

I/Oセクションは、入力チャネルを12本、出力チャネルを12本もっている。1つのチャネルにはMCU(Maintenance Control Unit)が接続されている。MCUはマシンの初期化、プログラムのロードや、いろいろな保守ツールを実行したりするもので、Data Generalの16bitのミニコンピュータが使われた。他のチャネルにはハードディスクなどのマスストレージやフロントエンドコンピュータ、各種の周辺装置が接続される。

そして、Cray-1のタワーの中の各シャシーのプリント板の配置は、図1.39のようになっている。この図に見られるように、プロセサのロジックは中央の8シャシーに搭載されており、両端の16シャシーにはメインメモリが搭載されている。

(次回は7月13日に掲載します)