メニーコアプロセサの電源制御

現在、商品化されているTileraのTile-GxプロセサについてはDVFSや電源スイッチなどの電源制御に関する記述は見られず、このような機能は実装されていないと思われる。

一方、IntelのXeon Phi 5110PプロセサはDVFSやターボモード、コア(とVPUのペア)のクロックオフ、電源オフなどの機能を持っているが、最大負荷のコアの動作状態をベースに決めた電源電圧やクロックを全コアに適用しており、コアごとの電源オフは行われていない。

このように、メニーコアプロセサの電源制御のレベルは、マルチコア以下という状況である。これは、これらのメニーコアプロセサは全コアがほぼ同様に動くような使い方を想定しているので、電力制御としては全体をまとめてシングルコアのように考えているからではないかと思われる。また、現在のメニーコアチップは集積するコア数を増やすのが第一で電源制御にチップ面積を割く余裕がない、というのもその理由ではないかと思われる。

NVIDIAのTegra 3

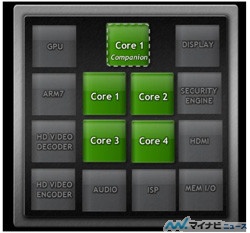

NVIDIAのTegra 3は、4コアのARM Cortex A9コアとGPUやその他の回路を集積したSoC(System on Chip)で、GoogleのNexus 7タブレットなどに採用されている。このTegra 3は、図8.3に示すように、Core 1~4に加えてCore 1 companionと書かれたコンパニオンコアが搭載されており、5コアのマルチコアプロセサとなっている。なお、すでにTegra4が発表されており、コアがCortex A15に変更され、GPUが大幅に強化されているなどの違いはあるが、ここのテーマであるDVFSによる省電力化の観点ではTegra3と変わりはない。

|

|

図8.3 4+1コア NVIDIAのタブレット向けTegra 3の内部構成。中央のCore 1~4が高性能コア。その上のCompanionコアは省電力用コア (出典:NVIDIAのTegra Whitepaper) |

処理負荷が重い場合は、Core 1~4を使うが、処理量が減ってくると使用するコア数を減らし、不要なコアの電源スイッチをオフにする。さらに処理量が減ると、Core 1だけを使い、DVFSで負荷に合わせて電源電圧を下げていく。ここまでは、通常のマルチコアプロセサの制御と同じであるが、Tegra3では、必要な性能がCore 1をDVFSで最低のクロックにしても処理能力が余ってしまう場合は、Core 1のプログラムカウンタやレジスタなどの状態をコンパニオンコアにコピーして、処理をコンパニオンコアに移す。

一方、処理負荷が増えてきてコンパニオンコアでは対応できなくなってくると、プログラムカウンタやレジスタの状態をCore 1にコピーして処理を高速コアに戻してやり、さらに負荷が増えるとCore 2~4を使っていく。

図8.4はTegra 3のチップ写真で、中央の5個の黄色の部分がCortex A9コアである。この写真で見る限りでは5個のコアに差はなく、コンパニオンコアも通常コアと同じレイアウトである。しかし、通常コアはTSMCの40Gと呼ばれる速度は速いがリーク電流も多いトランジスタを使っているのに対して、コンパニオンコアは40LPという速度は遅いが、リーク電流は1/10かそれ以下というトランジスタを使っている。

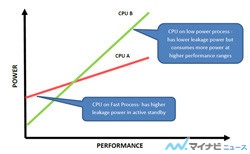

NVIDIAのホワイトペーパーには図8.5が載っており、高速トランジスタを使う通常コアのCPU Aは性能が低い状態でも多くの電力を必要とするが、性能向上に伴う電力の増加は緩やかである。一方、低電力プロセスのトランジスタを使うコンパニオンコアCPU Bは性能が低い状態の電力は少ないが、高い性能を必要とする場合の消費電力は通常コアよりも大きくなると説明されている。つまり、両者の線の交点より高い性能を必要とする場合はCPU Aを使い、それ以下の性能で良い場合にはCPU Bを使うことにより性能/電力を改善することができる。

タブレットやスマホなどでは、操作をしていないアイドル状態の時間が長いが、この状態でもCPUをすべて止めてしまうわけには行かないが必要な性能はほぼゼロで、図8.5のグラフの左端の状態の時間が長い。従って、コンパニオンコアを使うことによる電力低減と電池寿命の延長は大きな意味があり、マルチコアを低負荷時の電力削減に使った注目すべき技術である。