低性能プレーナーMX2FETから得られた知見

2D材料のテンプレート成長とレイヤートランスファーは、300mmウェハ上に400℃未満の温度で高品質の2D材料層を堆積するアプローチである。テンプレート成長では、事前に定義されたテンプレートとなる基板(サファイアなど)を使用して、2D材料の成長を単一の結晶方向に導いた後、300mmウェハ表面全体に広がる極薄層を破損することなくターゲットウェハに移送する必要がある。

2024のVLSI Symposiumにてimec、は300mm MX2ドライ転写プロセスフローを実証したことを報告した。これにより、99.5%を超すウェハ上の優れた均一性を備えた再現可能なプロセスが実現された12)。さらに、他のレイヤーアプローチと比較して、欠陥の数も減少することが確認された。

これらの結果を得るための鍵は、高性能ボンディング中のbond front initiationと呼ぶ貼り合わせ手法と、一時キャリアのリリース中のphotonic debondingと呼ぶ手法の採用である。bond front initiationは、最初にウェハの中心に結合力を適用することに基づいており、それがエッジに向かって伝播する技術。これにより、ボイド形成が軽減され、ボンディングの均一性が向上し、残留物がほとんどまたはまったく発生しないことが示された。

-

imecの300mm MX2ドライトランスファープロセスフロー(bond front initiationとphotonic debondingを含む)。このテストビークルでは、Si/SiO2がMX2成長テンプレートとして使用された (2024 VLSI Symposiumで発表)

これにより、レイヤートランスファは2D材料堆積の実行可能なオプションになる。提案されたプロセスフローは、3D SoCおよびチップレット統合のコンテキストで、チップ業界でよく知られている300mm互換の製造ステップを使用する。

実験室ベースのGAAナノシートにレイヤートランスファーを適用

imecでは、平面デバイスでのレイヤートランスファーから得た知識をGAAナノシートテストべヒクルに適用した。その結果、ラボベースのMX2nFETは優れた適合性、均一性、層品質を備えていることがわかった。層転写はナノシートチャネル形成(つまりCFET)にとって興味深いアプローチであり、600℃未満の温度で行うのが望ましい。

さらに、2024年のIEDMにてimecは300mmターゲットウェハ上にレイヤートランスファーによって堆積された単層MoS2チャネルを備えた機能的な積層ナノシートFETを報告した。このデバイスは、最先端のデバイスと比較して、同等のIon(約451μA/μm)と記録的なオンオフ比(>109)を示している。平面デバイスに基づく学習結果は、ゲートモジュールを含む重要なモジュール開発に使用された13)。

imecは低温での2D材料の直接成長を研究しており、これにより、より小さな選択された領域に堆積した場合にのみ高品質の層を実現できる可能性がある。

2Dベースの平面pFET向け300mm統合プラットフォーム

2023年のIEDMでは、imecがIntel共同で、MoS2nFETと同様のプロセスフローを使用して、300mmの集積プレーナーWSe2pFETトランジスタを初めて実証した14)。imecチームはまた、粒子サイズがデバイスの性能と信頼性に与える影響を調べて報告した。

信頼性の向上と変動性の低減への道

過去数年にわたってimecとウィーン工科大学(ティボール・グラッサー教授のグループ)は、 2D材料ベースのデバイスの信頼性と変動性の定量化において研究を進めてきた。例えば、2D層の厚さ、結晶粒のサイズと方向、2D成長テンプレートが300mmの統合MX2平面デバイスの性能に与える影響を研究してきた。その結果、信頼性と変動性の問題の根本原因の特定につながり、現在はその解決に向けた取り組みが進められている15)。

残された課題への取り組み

2D材料のデバイスへの適用に関しては、世界中のさまざまな研究グループによって大きな進歩が遂げられているが、先進ノードでの大量生産に向けてのギャップを埋めるには、まだいくつかのブレークスルーが必要である。

imecは、ファブ互換のソース/ドレインコンタクト形成、制御可能なドーピング、 MX2デバイスによるCMOSの有効化(つまりp型とn型のFETの統合)が、今後の最も重要な障害であると認識している。これらの問題を解決するには、業界リーダー、大学グループ、研究機関、ツール開発者が参加する共同作業が必要である。

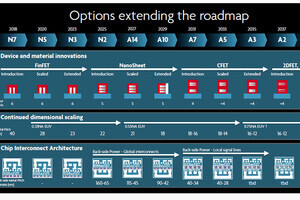

これらの問題が解決されれば、2D材料の将来は明るくなる。2D材料は、 A7以降のロジックスケーリングロードマップを前進させるだけでなく、その特性により、ロジックをはるかに超えてアプリケーション領域を拡大することもできる。例えば、オフ状態電流が極めて低いという利点を活かして、組み込みDRAMアプリケーションの可能性も示唆されている(おそらくA7ノード以降)。さらに、まるで表面輸送のような2D材料の輸送特性は、非常に簡単に変化させることができるため、確率コンピューティングや機械学習アプリケーションにも最適といえる。

本記事はimecの技術解説記事「Introducing 2D-material based devices in the logic scaling roadmap」をimecの許可のもと、翻訳・改編したものとなります

参考文献

[12] “EOT scaling via 300mm MX2 dry transfer – Steps toward a manufacturable process development and device integration”、S. Ghosh et al., 2024 VLSI Symposium

[13]“High-performance monolayer-2D stacked nanosheet FETs with high ION ~451μA/μm and ION/IOFF>109”F. Xi et al., 2024 IEEE International Electron Devices Meeting (2024IEDM)

[14]“Exploring manufacturability of novel 2D channel materials: 300mm wafer-scale 2D NMOS & PMOS using MoS2, WS2, & WSe2”、C.J. Dorow, T. Schram et al., 2023 IEEE International Electron Devices Meeting (2023IEDM)

[15] “「Evidence of contact-induced variability in industrially-fabricated highly-scaled MoS2 FETs”L. Panarella et al., npj 2D Materials and Applications、Volume 8, Article number: 44 (2024)

César Javier Lockhart De La Rosa(セザール・ハビエル・ロックハート・デ・ラ・ロサ)

Gouri Sankar Kar(ゴーリ・サンカル・カル)