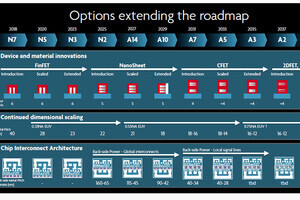

ベルギーの最先端半導体研究機関であるimecの最新の半導体ロードマップによれば、2030年代に1nm(=10オングストローム)未満の技術ノードが採用されるようになるとロジックトランジスタのアーキテクチャはナノシートからCFET(Complementary Field Effect Transistor:相補型電界効果トランジスタ)に替わることが予想されている。

従来のCMOSトランジスタはスタンダードセルを構成するPMOS/NMOSトランジスタが横並びにならんでいるが、CFETではPMOS/NMOSを垂直方向に積み上げて配置することで、専有面積を小さく、効率を向上することができる。

高度なCFETアーキテクチャの伝導チャネル部分に原子数層の極薄膜である2D(2次元)材料を導入することは、ロジック技術のロードマップをさらに拡張するための有望な選択肢になっている。2D材料は、世界中の企業や大学で研究され、かなりの進歩が遂げられているが、産業界での実用化に向けてはまだまだ研究の大きな進展が必要である。

今後、imecはコストと努力の障壁を減らすために、ロードマップよりもはるかに早い段階で、性能がまだ十分ではないながら、平面2D材料をロジック半導体(デバイス)のチャネル材料として採用するという独自のアプローチを採用することにしている。

この連載では、imecの2D材料研究者が、2D材料をCFETに集積するための課題、最先端の遷移金属ジカルコゲニド(MX2)デバイス、imecの2D材料戦略、そして世界的なコラボレーションの必要性などについて解説していく。

シリコンベースのロジック半導体における微細化ロードマップ

ムーアの法則に触発されたトランジスタ回路のスケーリングは、もはやCMOSテクノロジノードの進化を予測する唯一の指標ではないことは、20年近く前から明らかになっている。

最初の兆候は、技術ノード間のパフォーマンス向上が鈍化し始めた2005年ごろに現われた。半導体業界は、パフォーマンス/電力/面積/コスト(PPAC)のメリットを維持するために、リソグラフィ中心のスケーリングを徐々に他の技術革新で補完し始めた。トランジスタレベルでの材料とアーキテクチャの探究、標準セルレベルでの設計とプロセステクノロジの同時最適化、 3D集積テクノロジによって可能になるシステムと設計とプロセステクノロジの同時最適化(STCO:system-technology co-optimization)などである。

トランジスタレベルでは、スケーリングによる性能低下は短チャネル現象に起因している。ゲート長の大幅な短縮と伝導チャネルの短縮の組み合わせにより、ゲートに電圧が印加されていない場合でもリーク電流が増加してしまう。同様に、縮小するチャネル領域に対するソースとドレインの影響も劇的に増大する。

これらの短チャネル効果により、チップ業界はプレーナMOSFETからFinFETへ、そして最近ではゲート・オール・アラウンド(GAA)ナノシートトランジスタへと移行しつつある。

これらのアーキテクチャの革新により、ゲートは伝導チャネルに対する静電制御を取り戻すことができた。ナノシートトランジスタファミリは、標準セルレベルの革新と組み合わせることで、少なくとも3世代のテクノロジで微細化のロードマップを継続することが期待されている。これには、高度な相互接続およびミドル・オブ・ライン・スキーム、チップ裏面電源供給ネットワーク(BSPDN)の導入などが含まれる。

CFETは、次のゲームチェンジャーとなり、nチャネルとpチャネルを積み重ねることでさらに面積を削減できる。

imecは、A7ノード(いわゆる0.7nmあるいは7オングストローム)以降に導入されると予測しており、imecの技術ロードマップでは少なくともA3(3オングストローム)世代まで延長される。GAAナノシートトランジスタと同様に、ゲート(nチャネルとpチャネルに共通)は、Siチャネルの周囲とチャネル間を完全に包み込み、最大限の静電制御を保証している。

2D材料の登場

しかし、最終的には、CFETトランジスタの時代になっても、短チャネル効果により、さらなるスケーリングが再び複雑になる。トランジスタのゲートとチャネル長が継続的に短縮されるため、電流が流れる経路も比例縮小し、半導体チャネルをさらに薄くする必要がある。これにより、デバイスがオフになっているときに電荷キャリアが漏れる機会が制限される。CFETトランジスタを、伝導チャネル長が10nm未満のA2(いわゆる2オングストロームあるいは0.2nm)トランジスタ技術ノードに移行するには、Si チャネルの厚さも10nm未満に縮小する必要がある。しかし、このように薄いSiチャネルでは、電荷キャリアの移動度とトランジスタのオン状態電流が劇的に低下し始める。

ここで、2D半導体、特に遷移金属ジカルコゲニド(MX2)がチャンスを提供してくれる。MX2とは、遷移金属元素M(Mo、W、Nbなど)と2個のカルコゲナイドX(S、Se、Teなど)が結合した物質のことである。これらの半導体では、原子が層状結晶として配置され、単層の厚さはわずか約0.7nmであるため、非常に薄いチャネルが可能になる。さらに、チャネルの厚さに関係なく、比較的高いキャリア移動度を維持できる。これにより、短チャネル効果を心配することなく、究極のゲートおよびチャネル長のスケーリングが可能になる。

先端ノードにおける2D材料のCFETへの集積とその課題

2Dチャネル材料が究極的に超微細化ノードで実現する大きなパフォーマンスの飛躍は、この分野の大手半導体メーカーや学術団体リーダーの関心を刺激することとなっている。心強いことに、彼らは最先端のノードに2D材料を導入する際の障害を克服するために、研究開発に多額の投資を始めている。2D材料のトランジスタへの集積には確かに独自の様々な課題があり、A2ノード導入に向けたコストと集積の取り組みがさらに増加している。

2D材料の堆積

まず、2D材料層を堆積するという課題がある。高性能デバイスを必要とするアプリケーションの場合、以下の2つの主な方法がある。

- ターゲット基板上に2D材料を直接成長させる方法

- 理想的な「成長基板」上で成長させてから、その層をターゲット基板に移植する方法

2D材料の直接成長には通常、特定の基板が必要で、高温(約1000℃)で行われる。ただし、業界に適合したプロセスと材料が必要な場合、成長基板は高度な結晶化を誘発するのに理想的ではない可能性があり、フィルムのパフォーマンスが低下してしまう。とはいえ、直接成長は、適合性、ウェハレベルのカバレッジ、および量産用プロセスとの互換性を提供できる可能性がある。

2番目のアプローチでは、成長は外部の「理想的な」基板(サファイアなど)上で行われるため、高性能のフィルムを容易に作成でき、その後ターゲットウェハに移植できる。移植自体は、直接成長の場合よりもはるかに低い温度(約300℃)で実行できる。ただし、移植によってプロセスステップ数が増えると、チップ製造プロセスのコストと歩留まりに影響する可能性がある。

ゲートスタック集積

2つ目の課題は、ゲートスタック集積と誘電体堆積に関するものである。皮肉なことに、2D材料を非常に薄くできる理由そのものが、誘電体堆積を複雑にする原因でもある。2D材料を構成する層は、非常に弱いファンデルワールス力(vdW:van der Waals)によって垂直に互いに結合しており、表面はダングリングボンドなしでほとんど不活性化されている。これは、表面のダングリングボンドとの相互作用に依存する原子層堆積(ALD)など、Siで非常にうまく機能してきた堆積技術の使用を困難にしている。

近年、imecと大手半導体メーカーによって大きな進歩が遂げられており、ゲートスタックを集積したn型ナノシート2Dチャネルが実証されているが、主に研究室ベースのデバイス上で行われている1-6)。

低抵抗ソース/ドレインコンタクト

3つ目の大きな課題は、低抵抗のソース/ドレイン接点の形成である。Siの場合、ソース/ドレイン接点は、金属をソース/ドレイン領域に接触させて界面にショットキー障壁を作成することで形成される。その後、電荷キャリアをトンネル効果によってソースに注入できる。低抵抗のソース/ドレイン接点を実現するために、以下の2つの重要な技術が適用される。

- ソース/ドレイン領域の高濃度ドーピング

- シリサイドの形成

ただし、これらの技術を2D材料の薄い層で実現するのは非常に困難であり、研究者は代替ソリューションの探索に駆り立てられている7-9)。

2D材料のドーピング

2D材料のドーピングは、低抵抗コンタクトを得るために重要であるだけではない。チャネルのしきい値電圧(Vth)を調整し、アクセス抵抗を減らすためにも必要である。3D材料とは異なり、従来のイオンビーム注入を使用した2D材料の置換ドーピングは、材料の輸送特性を大幅に低下させる。非常に薄いため、格子内の原子を1つ置き換えるだけでも、2D材料では3D材料よりもはるかに大きな影響がある。ほかのドーピング技術(静電ドーピングや表面ドーピングなど)も研究されているが、明確な解決策はまだ見出されてはいない。

p型およびn型FET

CMOS技術のアプリケーションは、nチャネルFETとpチャネルFETの両方の組み合わせに依存している。標準的な CMOS技術では、両方のタイプのFETを形成するためにSiが使用される。しかし、それを可能にする2D材料は今のところ見つかっていない。n型に使用される最適な材料(MoS2など)は、p型FETに最適な材料ではなく、WSe2が最も有望な材料である。

ファブでの集積と信頼性とばらつきの向上の必要性

最後に、最近まで研究は主に研究室で行われており、そこでは「ヒーロー」デバイスはcmスケールで形成されていた。しかし、プロセスを300mmウェハと互換性のある産業規模にするには、膨大な開発努力が必要である10)。並行して、信頼性の向上とばらつきの大幅な削減が必要である。

次回は、性能の低いデバイスへと2D材料を段階的に導入しようというimecのアプローチを説明していく。

本記事はimecの技術解説記事「Introducing 2D-material based devices in the logic scaling roadmap」をimecの許可のもと、翻訳・改編したものとなります

参考文献

[1]“First Demonstration of GAA Monolayer-MoS2 Nanosheet nFET with 410μA μ m ID 1V VD at 40nm gate length,”、Y. Chung et al., 2022 IEEE International Electron Devices Meeting (2022IEDM)

[2]“High Mobility TMD NMOS and PMOS Transistors and GAA Architecture for Ultimate CMOS Scaling,”、A. Penumatcha et al.、2023 IEEE International Electron Devices Meeting (2023IEDM)

[3]“Status and Performance of Integration Modules Toward Scaled CMOS with Transition Metal Dichalcogenide Channel,”、A. Chou et al., 2023 IEEE International Electron Devices Meeting (2023IEDM)

[4]“Monolayer-MoS2 Stacked Nanosheet Channel with C-type Metal Contact”、Y. Chung et al., 2023 IEEE International Electron Devices Meeting (2023IEDM)

[5]“Dual gate synthetic WS2 MOSFETs with 120µS/µm Gm 2.7µF/cm2 capacitance and ambipolar channel、D. Lin et al.、2020IEEE International Electron Device Meeting(2020IEDM)

[6]“Scaling synthetic WS2 dual-gate MOS devices towards sub-nm CET”、D. Lin et al.、2021 VLSI Symposium

[7]“Yttrium-doping-induced metallization of molybdenum disulfide for ohmic contacts in two-dimensional transistors”、Jiang, J., Xu, L., Du, L. et al., J. Nature Electronics, Vol.7, pp.545–556 (2024)

[8]“Antimony Semimetal Contact with Enhanced Thermal Stability for High Performance 2D Electronics”、A.-S. Chou et al., 2021 IEEE International Electron Devices Meeting (2021IEDM), San Francisco, CA, USA, 2021, pp. 7.2.1-7.2.4

[9]“Advancing 2D Monolayer CMOS Through Contact, Channel and Interface Engineering”、K. P. O'Brien et al.、 2021 IEEE International Electron Devices Meeting (2021IEDM), San Francisco, CA, USA, 2021, pp. 7.1.1-7.1.4

[10]“Process integration and future outlook of 2D transistors”、K.P. O'Brien, Nature Communications、volume 14, Article number: 6400 (2023)

César Javier Lockhart De La Rosa(セザール・ハビエル・ロックハート・デ・ラ・ロサ)

Gouri Sankar Kar(ゴーリ・サンカル・カル)