東北大学は12月10日、「確率論コンピュータ」に必須と考えられていた、デジタル信号をアナログ信号化する回路D-Aコンバータ(DAC)を不要とする完全デジタル方式の「確率ビット(Pビット)回路」を提案し、熱で磁化方向が確率的にゆらぐスピントロニクス素子を用いてその動作を実証したと発表した。

同成果は、東北大 電気通信研究所の深見俊輔教授、同・金井駿准教授、同・金子遥南大学院生、同・大野英男特別栄誉教授、米・カリフォルニア大学サンタバーバラ校のケレム・カムサリ博士らの国際共同研究チームによるもの。詳細は、12月6~10日に米・サンフランシスコで開催されたIEEE主催の電気デバイスの国際会議「2025 IDEM」で発表され、その論文とビデオプレゼンテーションが公式サイトで公開された。

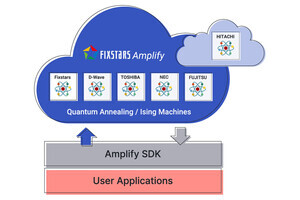

確率論的コンピュータの大規模化に光

現在のコンピュータは、情報を0か1で表すビットを用い、逐次的に計算を行う決定論的なコンピュータである。しかし、「巡回セールスマン問題」に代表される組み合わせ最適化問題など、実社会で求められている計算は不得手だ。その解を短時間で得られる可能性があることから、世界中で量子コンピュータの高性能化が進められている。だが実用的な大規模な量子コンピュータを実現するには、ノイズに強い誤り耐性の仕組みを持つ必要があり、その実用化まではまだしばらくの時間がかかると予想されている。

こうした背景から現在注目されているのが、確率論コンピュータだ。このコンピュータは、熱的ゆらぎなどの物理状態による確率的なゆらぎをハードウェアレベルで利用し、確率的に0または1を出力するPビットで構成され、多数の状態を並列的に探索する仕組みを持つ。量子コンピュータの量子ビットは、0と1の重ね合わせを扱うのに対し、Pビットはそれとは異なる原理のコンピュータだといえる。確率論コンピュータはGPUなどの汎用コンピュータよりも高効率に動作する可能性があることに加え、現行の半導体集積回路製造技術との親和性が高く、近い将来の新たな計算基盤として期待されている。

しかし、これまで提案されていたPビットには1つの大きな弱点があった。それは、0と1の出力確率を制御するための入力信号がアナログであるため、専用のDACが必要なことだ。DACは面積が大きく消費電力も多いため、数千以上の規模のネットワークを構築しようとするとボトルネックとなることが危惧されていた。

なお、DACの使用を避けるため、他のアナログナノデバイスを併用するという手段も考えられているというが、複数のナノデバイス技術を同時に成熟させる必要があるため、大規模誤り耐性量子コンピュータと同様、実現時期がしばらく先になってしまう可能性が高くなると見られている。そのため、アナログ回路を使わずにPビットを制御する「完全デジタル方式」が求められていた。そこで研究チームは今回、その実現を目指したという。

今回の研究で提案された完全デジタル方式のPビット回路では、単純なデジタル回路を段階的に結合した回路にスピントロニクス素子由来の乱数を入力し、読み取り用のデジタル回路でPビットへのデジタル入力に応じた結果を出力するという仕組みだ。

-

従来型Pビット(a)と、今回提案されたDAC不要のPビットの回路構成模式図。Xは状態が確率的にゆらぐデバイスを表し、今回は熱で磁化方向が確率的にゆらぐスピントロニクス素子が用いられている。従来型では、DACが必要だったのに対し、今回のPビットは遅延回路などのデジタル回路のみで構築されており、確率論的コンピュータの大規模化が容易だ(出所:東北大プレスリリースPDF)

この方式の特徴は、大規模なアナログ回路なしにPビットの0/1の出力確率を連続的に調整できる点だ。さらに、スピントロニクス素子を構成する磁石のある時刻と別時刻での磁化の方向の相関が、時間間隔が長くなるほど小さくなることを利用し、デジタル遅延回路の遅延時間を調整することにより、内部パラメータの書き換えなしに、系の擬似的な「温度」を制御することにも成功したとする。

さらに今回の研究では、スピントロニクス素子の磁化の緩和時間のばらつきや、0と1の出力比の微小な偏りといった実デバイスに不可避な問題が、遅延時間の調整や排他的論理和(XOR)演算により解消できることも判明した。この結果、複数の性質の異なるデバイス間で統一された入出力特性を得ることができ、これによって拡張性の高い回路設計が可能になったとした。

-

緩和時間というゆらぎの特徴的な時定数が異なるスピントロニクス素子を用い、今回の提案回路で構築されたPビットの入出力特性。素子の特性ばらつきの補正前(a)、ばらつき補正後(b)の測定結果。補正によって均一な入出力特性が得られていることがわかる(出所:東北大プレスリリースPDF)

原理実証実験としては、今回の提案回路からなる複数のPビットを用い、スピングラスのエネルギー最小状態を探索するという組み合わせ最適化に成功したとのこと。ここでは、遅延回路の遅延時間を変化させることで、徐々にネットワークの「温度」を変化させる「オンチップアニーリング」と呼ばれる技術が提案された。

-

今回のPビット回路を用いて組み合わせ最適化問題をアニーリングで計算した結果(例題は、8x8x8=512スピンの三次元スピングラス問題)。回路内の遅延時間を徐々に変化させることでPビットの実効的な「温度」を変えられることを利用し、徐々に系の「温度」を冷やすことで基底状態に収束すること、つまり、最適な組み合わせを計算できていることが確認された(出所:東北大プレスリリースPDF)

今回のDACが不要なPビットは既存の半導体製造技術との互換性に優れ、AI計算、機械学習、組み合わせ最適化などを高効率に処理するハードウェアとしての応用が期待される。研究チームは今後、ネットワークの大規模化、デバイス技術の向上を推進し、実用性の高い確率論コンピュータの実現を目指すとした。今回の成果は、大規模拡張性に優れた確率論コンピュータの社会実装へと近づける重要なステップといえるとしている。