PCIe 8の目標帯域が正式に判明

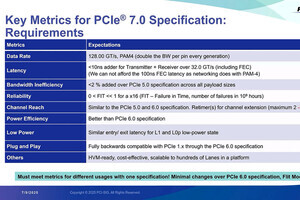

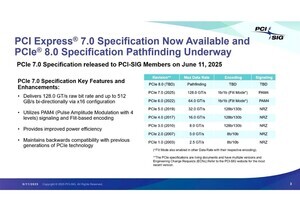

6月11日にPCI Express 7.0がリリースされた際には、PCI Express 8.0に関してはPathfindingという状況が示されていた事はすでに報じたとおりだが、「FMS(Future Memory Summit) 2025」にて開催された説明会で、PCI Express 8.0が正式にPCI Express 7.0の倍の帯域を目指すことが明らかにされた(Photo01)。

ここで公開されたのはあくまで帯域が2倍になるという話で、EncodingはFlit Modeを使いSignalingはPAM4のまま、という事になる。

金属配線なのか光ファイバーなのか

これに関してPCI-SIGに「Is it correct to understand that PCI-SIG plans to build PCIe 8.0 based on electrical signals?」という質問を送ったところ、その返事は「We can use similar techniques that we used on PCIe 7.0, but we will also have optical options」という、なかなか捻くった返事が戻ってきた。

ここから考えると、

- 電気信号ベースである事は変わらないと思われる。

- でも速度を倍にするとは限らない(少なくとも速度に関して異様なほどに触れていない)

ということが判る。

冷静に考えても、現在の速度を倍にすると128GT/secのPAM4である。200G Ethernetの100GT/sec PAM4よりもさらに条件が厳しい訳で、これ普通にFlitでカバーしようとすると再送頻度が相当増えてしまいそうに思える。だからといってEthernetのRS-FEC(544,514)を搭載したりしたら、Latencyと消費電力が激増する。

どうやって帯域の倍増を実現するのかを考える

となると、帯域を増やそうとすると信号本数を増やすしかない事になる。ここで「Reviewing new connector technology」が効いてくることになる。ここからは筆者の想像であるが、

- PCI Express 7.0までは2対4本(Differentialで、双方向)の配線が1Laneであったが、PCI Express 8.0では4対8本(Differential、双方向、2bit)で1Laneとする。

- PCI Express 8.0では、新しく倍密度のコネクタを利用する。図1がPCI Express 7.0までの、図2がPCI Express 8.0以降のコネクタとカードエッジ例である。これ、丁度ISAとEISAのコネクタとか、USB Type-AのUSB 2.0と3.0の関係に近い。PCI Express 8.0のカードをPCI Express 8.0のコネクタに装着した場合のみ1Laneが4対8本として動作し、それ以外の組み合わせでは1Laneが2対4本として動作する。

といったあたりを狙っているのではないかと思われる。別の案としては、1Laneは2対4本のままだが、ただし送信と受信を同じ配線で賄う(昔の電話とか、100BASE-TX方式)という案も無くはないが、64GT/secの配線でこれをやるのはかなり厳しいだろう。

この方式は、実は実装も難しくない。PCI Expressの階層構造で言うなら、Physical Layerの中のLogical Sub BlockとElectrical Sub Blockの間に1:2/2:1のMUX/DeMUXを入れてやるだけで済むからだ。上位層からすると、128GT/secのPAM4変調で転送されている様に見える(からFlitもこの単位で行われる)が、物理的には64GT/secのPAM4変調×2で実装されているという格好だ。なのでこの2bit分は連動して転送が行われることになる。これに起因するSkewの増加などをどう対処するか、といった事は今後考える必要があるだろうが、割と現実的な選択ではないかと思われる。