第9世代BiCS FLASH採用製品のサンプル出荷を開始

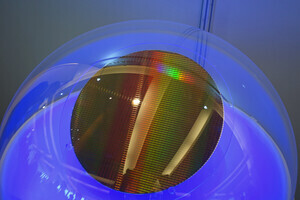

キオクシアは7月25日、第9世代のBiCS FLASH3次元フラッシュメモリ技術を適用した512GビットTLC(3ビット/セル)製品のサンプル出荷を開始したことを発表した。

同製品は、低容量から中容量帯向けで高い性能や優れた電力効率を必要とするアプリケーションをターゲットとして開発されたものとするほか、AIシステムにおいてGPUの使用効率最大化を狙うエンタープライズSSDなどにも展開していく予定ともしている。

既存セル技術と最新CMOS技術の融合で性能向上を実現

第9世代のBiCS FLASH技術は、ウェハボンディング技術を用いて、別々に製造したCMOS回路のウェハとメモリセルアレイのウェハを貼り合わせるCBA(CMOS directly Bonded to Array)技術を活用し、既存のセル技術(第5世代の112層ならびに第8世代の218層)と最新のCMOS技術を融合させ、投資コストを抑えつつ高性能を実現したもの。

今回、サンプル出荷が開始された製品は、第5世代BiCS FLASH技術をベースとした120層積層プロセスのメモリセル技術と、最新のCMOS技術を活用したものだという。これにより、既存の製品である第6世代技術を採用した512GビットTLC製品比で、書き込み性能は61%、読み出し性能は12%向上したとするほか、電力効率も書き込み時に36%、読み出し時に27%改善したとする。また、Toggle DDR6.0インタフェースの導入により、3.6GbpsのNANDインタフェーススピードも実現したほか、平面方向の縮小技術を組み合わせることで、ビット密度を8%向上したともしている。この512GビットTLCでは、NANDインタフェーススピード4.8Gbpsまでの動作も検証しており、今後市場要求に応じて製品のラインアップを検討していくとする。

第10世代の開発も進行中

なお、同製品の量産開始は2025年度中を予定しているほか、すでに積層数を増やすことで大容量化と高性能化を実現する第10世代の開発も進められているとしている。