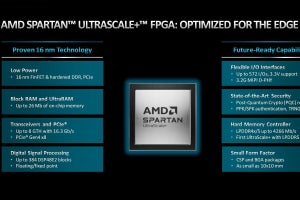

16nmプロセス採用のローエンドFPGA「Spartan UltraScale+」の出荷が開始

AMDは6月17日、TSMCの16nmプロセスを採用したローエンドFPGA「Spartan UltraScale+」の量産出荷を開始したことを発表した。

同シリーズは、高I/O、低消費電力で最先端のセキュリティ機能を必要とするコスト重視のエッジアプリケーション向けFPGAと位置付けられており、11Kロジックセル(LC)の「SU10P」から、218K LCの「SU200P」まで9製品が用意されている。

低LC構成の3製品が第1弾として出荷

今回、量産出荷を開始したのは、このうちLCがもっとも少ないSU10P、22Kの「SU25P」、36Kの「SU35P」の3製品。3製品ともにI/O数は最大304(SU200Pでは572)で、最少10mm×10mmのパッケージで提供される。

また、NIST承認アルゴリズムを使用したポスト量子暗号ハードIPを利用可能で、これにより高いセキュリティ性を提供するとしている。さらに、UltraScaleアーキテクチャに基づくI/Oタイル「XP5IO」により最大1.8Gbpsの低電圧差動信号(LVDS)、3.2Gbps MIPI D-PHY、およびその他の高速差動インタフェースをサポート。1.0~1.5Vの電源電圧で動作するXP5IOバンクを活用することで、LPDDR5のサポートが可能となっており、これにより32ビットインタフェースで最大4266MbpsをサポートするLPDDR4X/5統合コントローラを活用でき、最大15K LCの節約が可能となるため、設計者はより小型デバイスを活用することができ、電力とコストの削減を図ることができるとしている。

加えて、Octal SPIフラッシュメモリインタフェースによる迅速なコンフィギュレーションや、PCIe Gen4のハードIPによるサポート(エンドポイント/ルートポート両方の設計に対応)なども行われており、さまざまな用途においてコストの最適化を図っていくことが可能だと同社では説明している。

なお、同シリーズは同社が無料で提供する「AMD Vivado 2025 Design Suite Standard Edition」でサポートされており、シミュレーションから検証まで1ツールで実行することが可能である。