ルネサス エレクトロニクスは6月16日、次世代のIoTマイコンに向けた技術として、STT-MRAMの高精度ならびに高速読み出しを可能とする技術、ならびに書き換え動作を高速化する技術を開発し、22nmロジック混載MRAMプロセスを用いた32MビットMRAMメモリセルアレイ搭載のテストチップでの動作を確認したことを発表した。

同成果の詳細は、2022年6月12日から17日までハワイで開催されている「2022 IEEE Symposium on VLSI Technology & Circuits(VLSIシンポジウム2022)」にて、6月16日に発表された。

徐々に進む混載STT-MRAMの活用

一般的なロジック半導体の住み分けイメージとして、ローエンドがマイコン、ハイエンドがSoC/MPUといったものがあるが、近年、IoTの普及などに伴い、エンドポイント機器の処理性能の向上に対するニーズがでてきており、これたマイコンとMPUの中間のクロスオーバー領域を埋める製品が求められるようになってきている。こうした市場背景から、ルネサスに限らず、競合他社もこのクロスオーバー領域を埋める製品を投入するようになってきた。

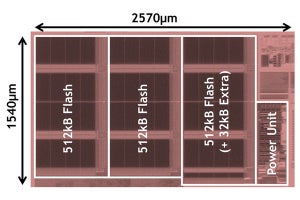

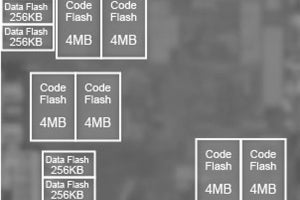

こうしたクロスオーバー領域に対し、BOMコストを抑えつつ、かつ従来からある組み込み開発環境でカバーしていくためには、マイコンそのものの高性能化と低コスト化が求められるようになっている。特にIoT向けなどのマイコンは一般的なロジックプロセスではなく、フラッシュメモリを搭載する混載プロセスが採用されてきており、40nmプロセス程度までのプロセスにはフラッシュメモリ混載プロセスが活用されてきた。しかし、28nmプロセス以下の微細プロセスにおける混載メモリを考えた場合、FEOLで形成されるフラッシュメモリよりも、BEOLで形成されるMRAMの方が開発が容易で、かつ製造コストを下げられるとして、混載MRAMの活用が徐々に進められつつある。

-

IoTに代表される分野でのエッジコンピューティングの活用ニーズが高まるにつれ、マイコンとMPUの間を埋める性能の製品が求められるようになってきている (資料提供:ルネサス。本レポートのすべてのスライドが同様)

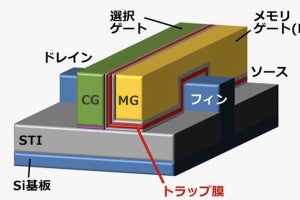

混載STT-MRAMの高性能化を妨げる課題

しかし、STT-MRAMを用いる場合、フラッシュメモリと比べ、スピン反平行状態(1)とスピン平衡状態(0)の状態間の抵抗比が小さいため、時間をかけて高精度な読み出しを行う必要があり、特に高温では状態間の抵抗比がさらに減少するため、高温動作時における対策も求められていたという。

具体的には、メモリセルが1の状態と0の状態の間の電流差が小さいと、データを読み分けるためのセンスアンプへの入力電圧差が小さくなり、センシングが難しくなるほか、放電時間を長くして電圧差を大きくしようとしても、センスアンプへの作動入力ノードがともに放電されきってしまうため、必要な電圧差が確保できないという課題があったという。

そこで今回の研究では、高精度なセンスアンプと適切な電圧レベルにブーストする回路(ブーストクロスカップルセンスアンプ回路)を開発、搭載することで、電圧がしきい値よりも低くなったタイミングでブーストを行い、センスアンプの入力電圧差(ΔVsa)を引き上げることで、必要な電圧差を確保しつつ高精度かつ高速な読み出しを実現したとする。

このアクセススピードは5nsほどとのことで、ブーストによって読み出し時間が伸びてしまうという気もするが、もともとMRAMの電流差が小さく、高精度測定のために読み出し時間を長く取る必要があったため、逆にトータルの時間としては短縮できるようになったという。