千葉工業大学(千葉工大)、東邦大学、中部大学の3者は2月15日、「カオス共鳴」を利用することで、メモリデバイスへの情報伝送にかかる消費電力を低く抑えることを可能とする機構を開発したことを発表した。

同成果は、千葉大 情報科学部 情報工学科の信川創准教授(国立精神・神経医療研究センター 精神保健研究所児童・予防精神医学研究部 客員研究員兼任)、東邦大 理学部情報科学科の我妻伸彦講師、兵庫県立大学大学院 応用情報科学研究科の西村治彦特任教授、中部大工学部 ロボット理工学科の稲垣圭一郎講師、福井工業大学 AI&IoTセンター/環境情報学部 経営情報学科の山西輝也教授らの共同研究チームによるもの。詳細は、IEEEが扱う全分野を扱うオープンアクセスジャーナル「IEEE Access」に掲載された。

世界的に増加するデータ量に対し、高密度かつ高速な伝送効率を低消費電力で実現するメモリデバイスの実現が求められており、その1つとして、しきい値特性を持つ非線形システムの弱入力信号に対する応答性が外部ノイズの影響で増大するという「確率共鳴」を用いた機構の研究が進められている。

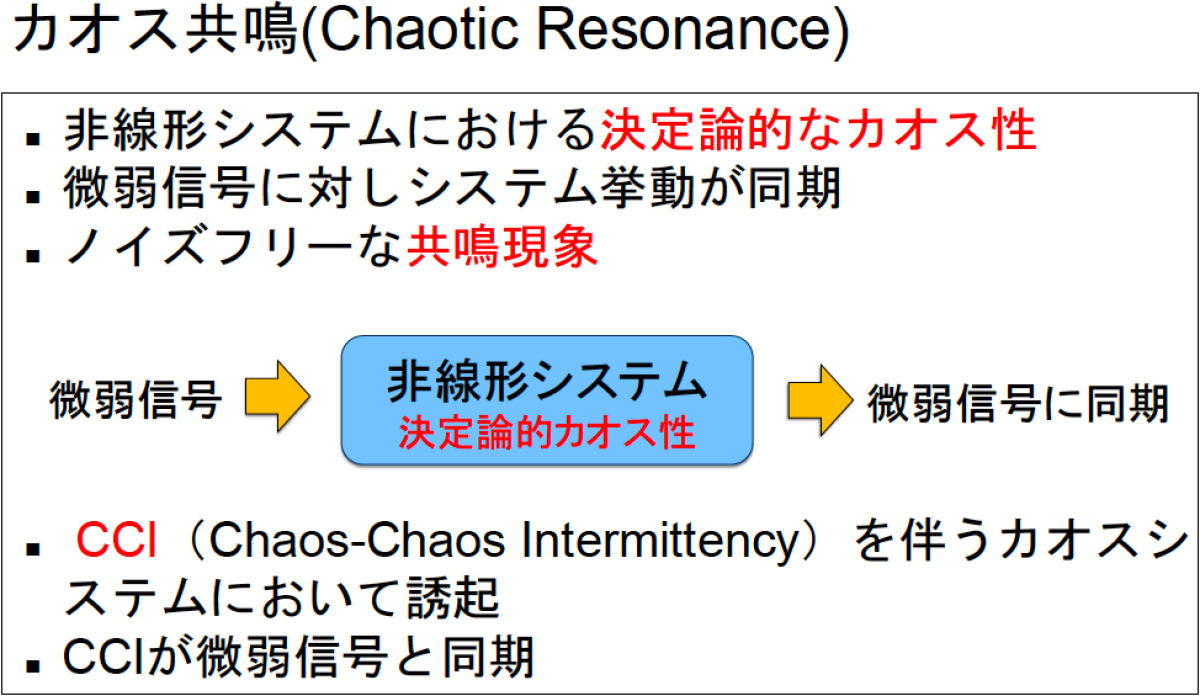

すでに確率共鳴を利用したメモリデバイス機構では、背景ノイズを利用することで、必要な伝送信号の強度を低く抑えることに成功しているほか、ゆらぎ源として外部からのノイズではなく、カオスによるシステム内部のゆらぎでも確率共鳴と類似した応答性の増強現象が生じること「カオス共鳴」では、確率共鳴よりもはるかに小さな入力信号に対しても鋭敏に応答することが知られていることから、研究が進められているという。

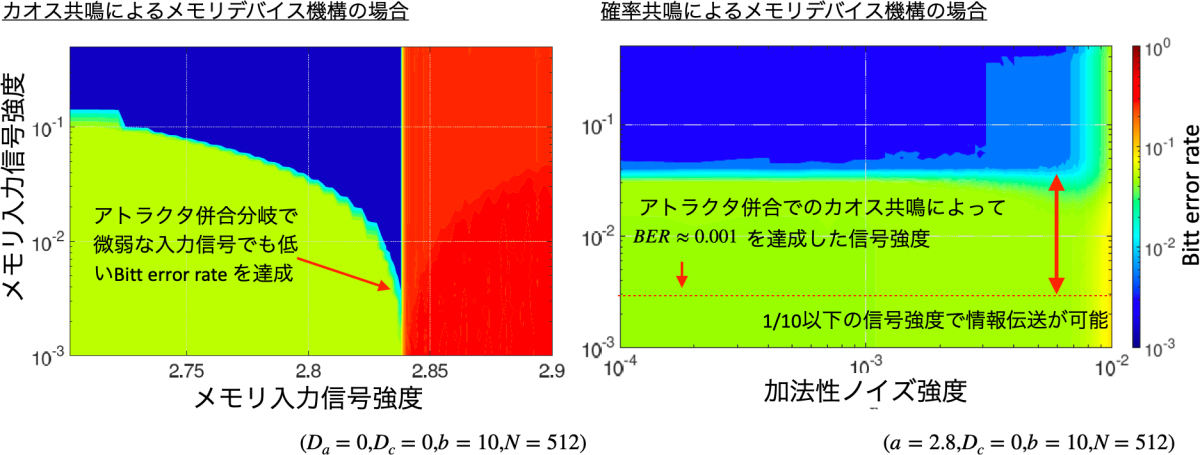

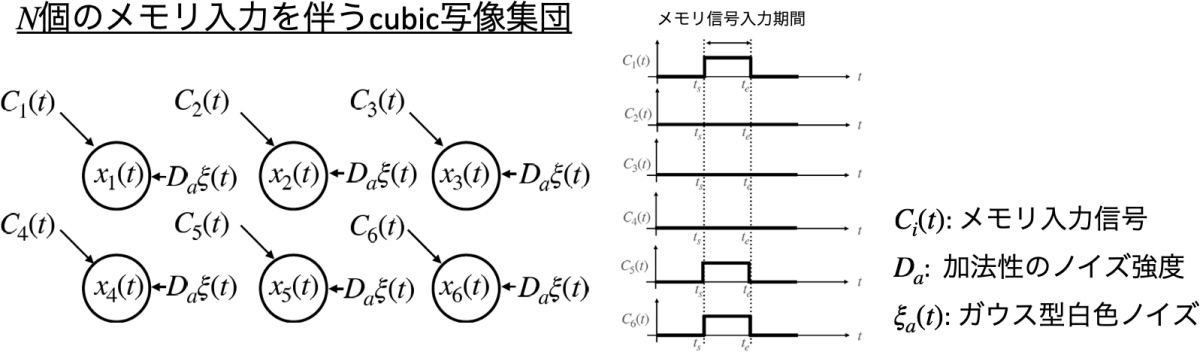

今回のメモリデバイス機構の開発では、「アトラクタ併合分岐」と呼ばれる複数の分離したカオス軌道が、システムのパラメータ調整により1つの軌道に併合され、間欠的にそれらの軌道を行き来する「カオス-カオス間欠性」特性を持つ「cubic離散写像システム」が用いられた。具体的には、512個のカオス-カオス間欠性を持つcubic離散写像の集団に対して、保存情報に対応する微弱な伝送信号を印加する実験がコンピュータシミュレーションを用いて実施。メモリ素子の状態遷移が正しく行われたか(正しくメモリへの書き込みが行われたか)をビットエラーレートで評価したところ、外部のノイズ印加を利用しないカオス共鳴によるメモリ機構の方が、ノイズを利用する確率共鳴によるメモリ機構よりも、1/10以下の微弱な信号強度でも情報を保存できることが判明したとするほか、この性能は、外部ノイズや各素子のパラメータのばらつきに対しても、一定の強度まで保持されることが確認されたとする。

-

512個のカオス-カオス間欠性を持つcubic離散写像の集団に対して保存情報に対応する微弱な伝送信号を印加するコンピュータシミュレーション実験が実施され、ビットエラーレートで評価された (出所:プレスリリースPDF)

今回、カオス共鳴によるメモリデバイス機構により、伝送信号の信号強度を低く抑えることに成功したが、研究チームでは、カオス性を持つ記憶素子に対し、回路駆動のためにどの程度の電力が必要であり、全体でどの程度の消費電力が削減できているのかについては、回路実装を含めた今後の研究が必要だとしている。すでに研究チームでは、カオス-カオス間欠性を持つカオスシステムに対してもカオス共鳴の生成に成功しており、今後はこのような非線形回路を用いた研究を進めていく予定としているほか、カオス共鳴による今回のアプローチが、世界のデータ増加に伴う消費電力増大の課題解決への一助となることが期待されるとしている。