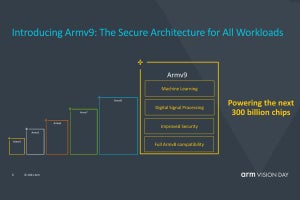

英Armは5月25日、Armv9-aに準拠したClient向けProcessor IPとして「Cortex-A510/A710」および「Cortex-X2」、それと新しいGPU IPとして「Mali-G310/G510/G710」を発表した。さらにこれを利用するためのInterconnectとして「CoreLink CI-700」および「CoreLink NI-700」を発表した。今回事前説明会が行われたので、その資料を基に概略をご紹介したい。

Armv9-aに準拠したIPが登場

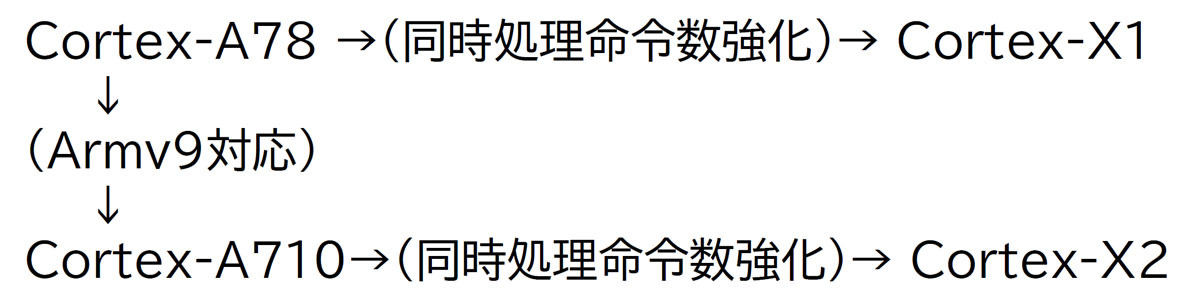

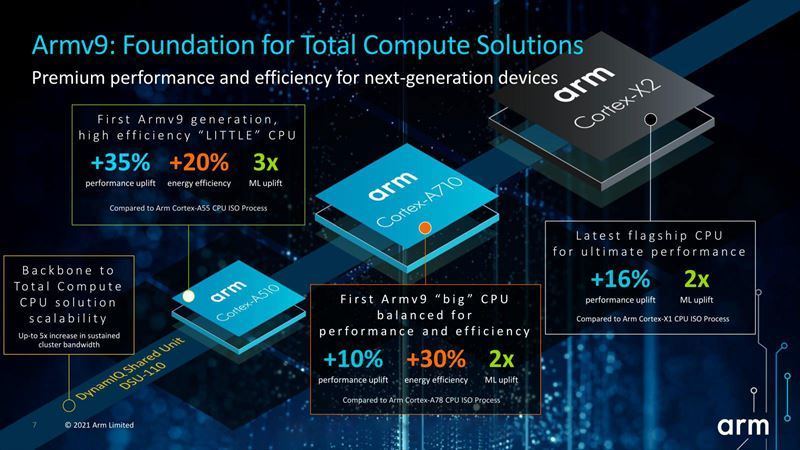

まずはProcessor IPについて。今回、ArmはClient向けとしてArmv9-a(恐らくArmv9.0-a対応と思われる)の3つのProcessor IPを発表した(Photo01)。

-

Photo01:「なんでCortex-A59とかCortex-79にしなかったのか?」と確認したところ、「ArmV9世代であることを明確に示したかったから」だそうである。でもそれならCortex-A61とかCortex-A81みたいな案もあった気もするのだが……

それぞれ、

- Cortex-A510:Cortex-A55の後継となるLITTLE core。Cortex-A55と同一条件で、平均性能35%アップ、エネルギー効率20%アップ、ML性能最大3倍

- Cortex-A710:Cortex-A78の後継となるbig core。Cortex-A78と同一条件で、平均性能10%アップ、エネルギー効率30%アップ、ML性能最大2倍

- Cortex-X2:Cortex-X1の後継となるハイエンドコア。Cortex-X1と同一条件で、平均性能16%アップ、ML性能最大2倍

をそれぞれ達成できる、としている。

この3つのコアはbig.LITTLEを構成可能であり、それもあってDSU-110というDynamIQ制御用のIPが別途提供されることになっている。big.LITTLEの場合、bigコアとLITTLEコアが同一のアーキテクチャである必要があり、それもあってbigとLITTLEの両方を刷新した形である。

さてそのCortex-A710とCortex-X2であるが、現時点では当然ながら内部の詳細などは明らかにされていない。ただCortex-X2に関して言えば、2020年のChromebook向けSoCと比較して、最大40%の性能アップと説明されている(Photo02)。

-

Photo02:zoomがここで出ているのは、例えばzoomのバーチャル背景設定を行おうとすると、Armだと8コア構成が必須で、しかもそれなりに演算性能が必要ということで、こうしたシーンで従来のChromebook向けSoCとCortex-X2ベースで明確に性能差が出しやすいということかと思われる

「恐らくは」という話で言えば、

といった形での構成になっているのではないかと思われる。

実際、Cortex-X2を組み合わせた3種混合のbig.LITTLE構成の場合、ピーク性能、連続性能、省電力性能のいずれも30%向上するとしている(Photo03)。

-

Photo03:すべてSVE2を実装といっても、例えばCortex-A510は128bit、Cortex-A710は256bit、Cortex-X2は256bit×2といった形で実装の詳細は異なっている可能性がある

ちなみにDecoderの幅は、L1 Cacheからだと5命令/cycle、Local Cache(MicroOp Cacheの意味だと思われる)からだと8命令/cycleで、これはCortex-X1の構成と同じである。ただしCortex-A710は同様にそれぞれ5命令/cycle・4命令/cycleであり、これはCortex-A78(6命令/cycle・4命令/cycle)から若干のグレードダウンである。ちなみにCortex-A510まで含めて3つのコアはいずれもSVE2とNeonに対応しており、あるいは30%という性能はNEON→SVE2による性能向上分も加味されている可能性はある。

ちなみに現状はまだCortex-A510/710/X2ともに発表の段階で、実際の提供開始は今年後半になる模様。またPOP IPはIPの提供と同時期にスタート予定で、ターゲットは5nmプロセスという話であった。

Armv9時代に対応するGPU/Interconnectも登場

次にGPU。今回、Mali-G310/G510/G710という3つのGPU IPが発表された。Mali-G710はMali-G78の後継にあたるハイエンド製品で、一方Mali-G310/G510はそれぞれMali-G31/G57の後継と位置付けられる模様だ。アーキテクチャ的にはValhallベースということで、細かい改良を積み重ねた結果がこの性能向上につながっているものと思われる。

-

Photo04:Mali-G710はValhallベースで、恐らくMali-G510もValhallベースと思われるが、Mali-G310がどうかは確認しそこなった。ただVulkanの性能を4.5倍、というあたりはBifrostからValhallに移行した気もする

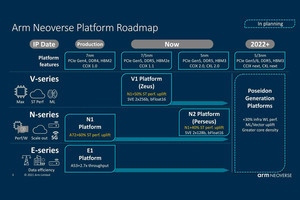

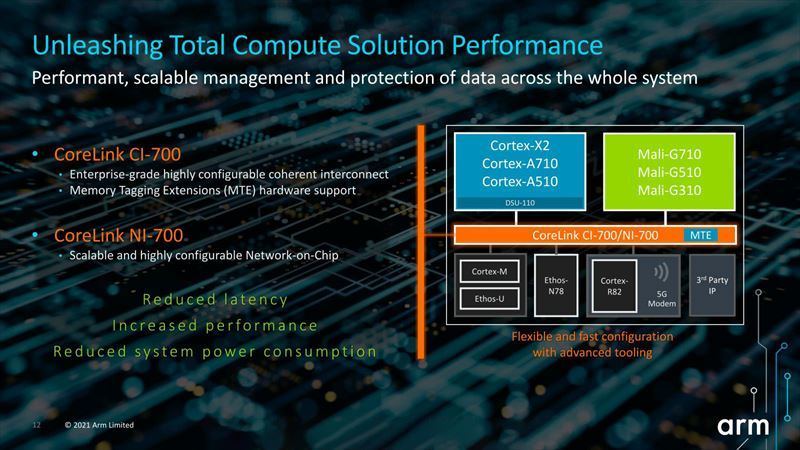

最後がInterconnect周り(Photo05)。

-

Photo05:big.LITTLEの最大コア数は依然として8のままだそうなので、NI-700も最大コア数は8のままと思われる。となると、今一つCI-700とNI-700の違いが見えてこないのだが、このあたりの詳細は後日明かされるのではないかと思われる

CI-700は従来のCCI-550の後継にあたると思われるもので、MTE(Memory Tagging Extensions)への対応をPTEに追加した点が変更点として挙がっているが、もちろんこれだけではないだろう。ちなみにMTEはArmv8.5-A/v9.0-Aから正式サポートされているので、このタイミングで追加されるのは理にかなっている。

一方のCoreLink NI-700については細かな説明が無かったが、名前からするとNeoverse向けのCMN-600をクライアント向けにしたような、いわばSubsetにあたるものかもしれない。

ご存じの通りCOMPUTEXが間もなくオンラインで開催され、多くのベンダーがここで新製品の発表を行うが、そのちょっと前にこれを公開、というのはCOMPUTEXのタイミングでどこかのベンダーがCortex-A510/A710ベースのSoCを発表する予定だから、というのが一番考えやすい案である。まぁSamsungかMediaTek、Qualcommあたりが何かしら出してきそうな気配はあるのだが、実際は蓋を開けてみるまで分からない。