2020年11月のSC20においてBlue Gene/L(BG/L)の開発に対し、Test of Time賞を授与された。Test of Timeは時の試練に耐えるという意味で、Blue Gene/Lの開発から約20年の年月が過ぎた今日から見ても、Blue Gene/Lは重要な意義があった開発であると認められたわけである。

SC20は新型コロナの蔓延で、全体がバーチャル開催となり、受賞記念講演もビデオ会議でのリモート開催であった。受賞記念講演を行ったのはIBMのJose Moreira氏と現在はOak Ridge国立研究所に所属するJeffrey Vetter氏である。Vetter氏は当時はLaurence Livermore国立研究所からBlue Gene開発チームに参加した。また、今回の授賞式の講演の中でも出席者から、IBMのAlan Gala氏の存在が大きいという発言があったが、Gala氏はこの表彰式には参加しなかった。

なお、バーチャルSC20は開催の6カ月後くらいまでは録画された発表ビデオを見ることができる。ただし、このビデオを見るには参加費(例年のリアル会議より大幅に安い)を払って参加登録を行う必要がある。

超並列で高性能を実現するBlue Gene/Lの思想

当時、1000~10000コアのシステムが出現していたが、Blue Gene/Lの提案のような超並列(130Kコア)システムは存在せず、これほどたくさんのコアをうまく利用することができるのか、これほどの多数のコアを持つシステムを故障なしに長時間動作させられるのかなどについて懐疑的なコメントが多かったという。

しかし、検討を進めていくと、アプリケーションのスケーラビリティーの問題も信頼度の問題も解決可能であることが分かってきたという。

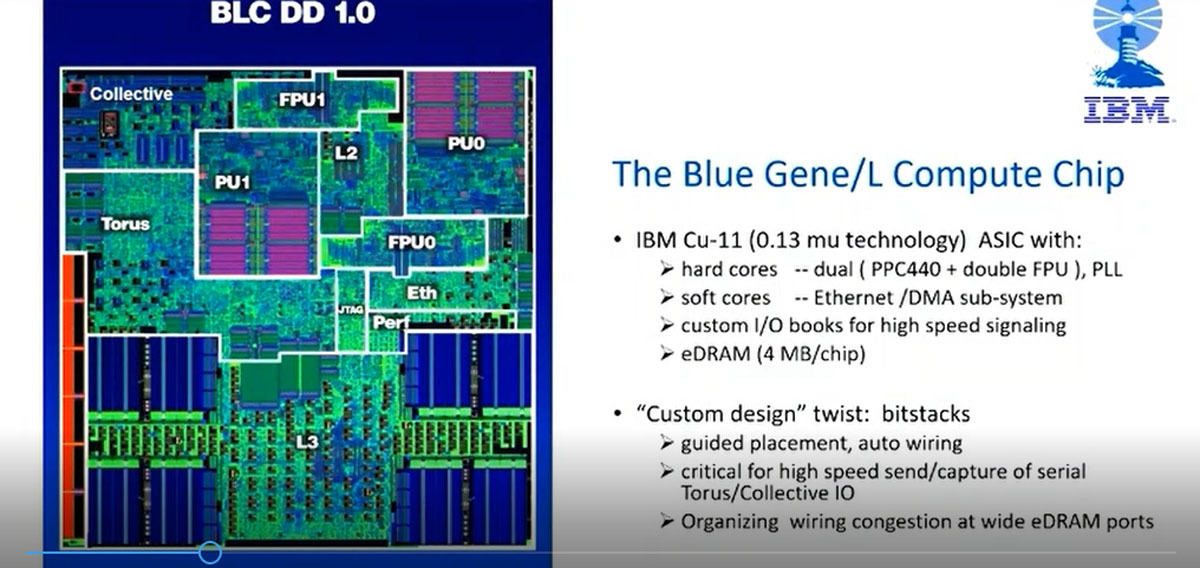

そして、PowerPC 440というPCクラスのCPUコアを利用し、科学技術演算に必須の64bitの倍精度浮動小数点演算器をCPUチップに追加した。このチップの演算性能は5.6GFlopsでチップの消費電力は15Wであった。

それまでスパコンと言えば、高性能のプロセサを並べるのが一般的であったが、BG/Lでは電力効率を重視し、PowerPC系の比較的簡素な設計のプロセサを使い、消費電力の小さいコンピュートノードを使った。

そして、4MBの組み込みDRAMを搭載しL3キャッシュとして使った。それに加えて、このチップはネットワークインタフェースも集積し、いわゆるSystem on Chip(SoC)のチップを作った。これにより、実装密度が上がり、ケーブルも短くなって、さらに消費電力を減らすことができた。

BG/LはCollectiveネットワークとTorusネットワークを持ち、Collectiveネットワークは、全チップを接続して、結果の合計を求めたりするもので、Torusネットワークは隣接するノードを3次元のトーラス型に接続し、必要に応じて隣接ノード間の転送を繰り返して任意のノード間のデータ伝送を行うネットワークである。

結果として、小さなCompute Boardに高密度設計の2ノードを詰め込んでおり、スパコンとして、高いFlops/床面積、高いFlops/W、高いFlops/$を実現している。

-

Blue Gene/Lのコンピュートチップのダイ写真。IBMの0.13μmテクノロジで作られ、PU0とPU1の2つのPowerPC 440のCPUコアを搭載。倍精度浮動小数点演算用のFPU0、FPU1を追加。4MBの組み込みDRAMを搭載 (SC20におけるTest of Time賞受賞記念講演資料をスクリーンショットしたもの。以下同様)

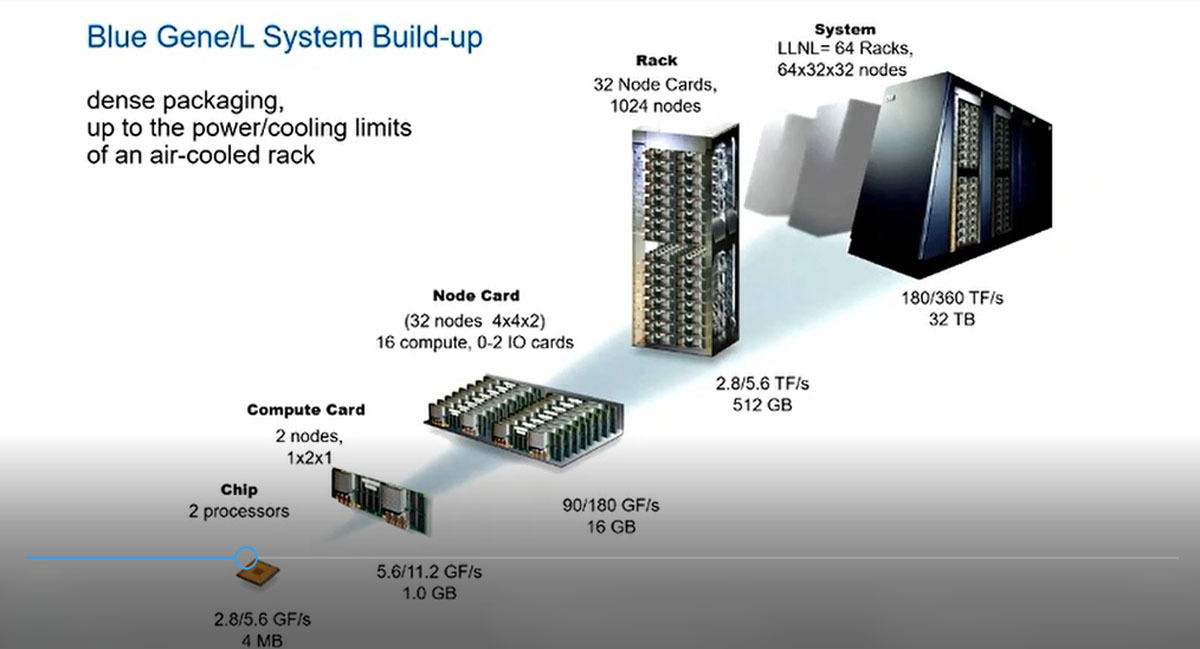

Blue Gene/Lのシステム階層

BG/Lシステムは次の図のような階層で作られている。左端の最初の階層は2コアのプロセサで、その次の階層のCompute Cardは1個のチップに2ノードを搭載していることになる。次の階層はNode Cardで16枚のCompute Cardと必要に応じて0~2枚のI/Oカードを搭載する。さらに32枚のNode Cardを1本のラックに収容している。

Compute Cardは2個のCPUを計算用に使った場合は11.2GFlopsのピーク演算性能を持っている。しかし、 1つのCPUだけを計算に使い、もう1個のCPUは通信などに使うという動作もできるように設計されている。このように使うと、演算性能は5.6GFlopsとなるが、通信などが計算に割り込んで同じ計算の実行時間がばらついてしまうことが避けられる。Compute CardはDRAMも搭載しており、搭載DRAMメモリは1.0GBである。

話は少し逸れるが、BG/Lでは部品数が多いので、部品の故障率を非常に気にして、DRAMメモリをDIMMに搭載してソケットに挿入するのではなく、Compute CardにDRAMチップを直接はんだ付けしていた。昔はプリント板の両面にプリント配線で接点を設けて接続するカードエッジ型のコネクタは接触不良が多く、故障率が高かった。

そして、Node Cardは演算性能180GFlops、メモリ容量16GB、Rackの演算性能は5.6TFlopsで512GBメモリを搭載している。

ローレンスリバモア国立研究所のBG/Lは、このラックが64本並んでいるので、システム全体の演算性能は360TFlops、搭載メモリは32TBとなっている。BG/Lは空冷で、空冷の限界までプロセサとメモリを詰め込んでいる。

-

Blue Gene/Lはプロセサチップ、Compute Card、Node Card、Rack、システムの階層で作られ、全体で64Kノードでピーク360TFlopsの計算能力と32TBのメモリを持っていた。比較的低電力のプロセサを使ったが、高密度実装であり、空冷のラックとしては冷却限界であった

プロトタイプ機や最初のシステムが順調に動作

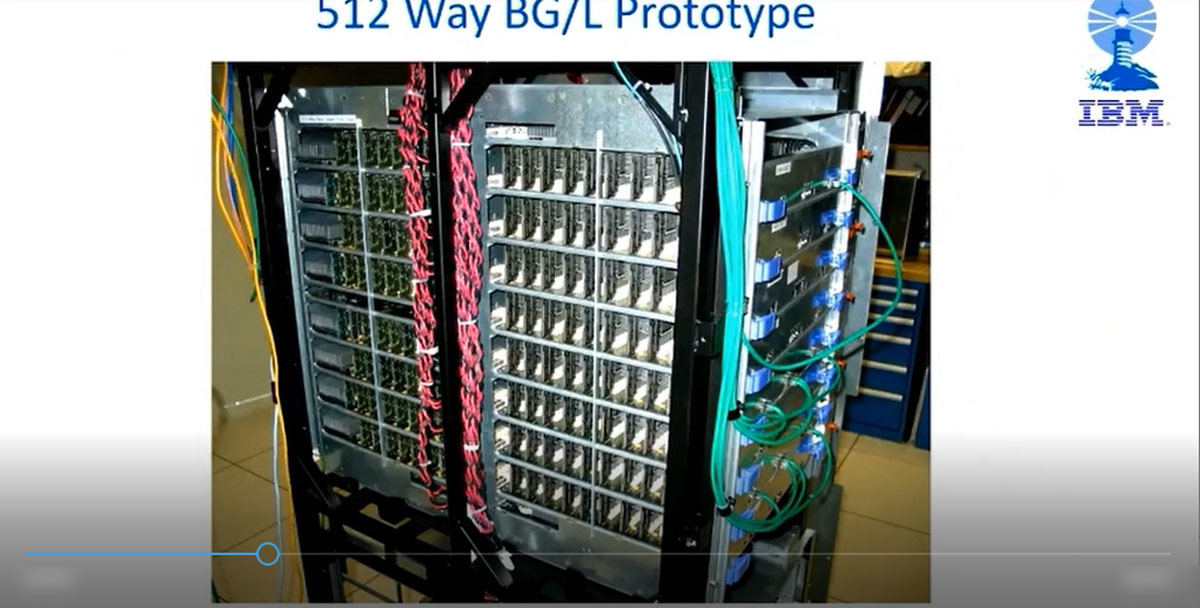

次の写真に写っているBG/Lのプロトタイプが出来、2003年6月23日に初めて電源を投入すると、チップは反応して最初のプログラムが問題なく動作した。その後、次々と大きいプログラムを動作させて行ったが、いずれも問題なく動作したという。

その後、ローレンスリバモア国立研究所のシステムの64ラックのシステムの構築が2003年11月に始まり、このシステムが2004年11月に32Kコアで70.72TFlopsのLINPACK性能を出してTop500の1位になる。

その半年後の2005年6月には64Kコアで136.8TFlopsとスコアを伸ばし、2005年11月にフルシステムの128Kコアで280.6TFlopsを達成した。

なお、このシステムは2007年には204ラックに拡張されて478TFlopsのLINPACK性能を達成している。

Blue Gene/Lの設計思想が正しいことが証明された

発熱が主要な問題となってきたスパコンにとって、電力効率の高いCPUコアを使って、より少ない電力で性能を上げなければ、消費電力が壁となるのでシステムの性能を高めることはできない。また、多数の部品を使って大規模な並列マシンを造り、それが故障せず、かつ、ハードウェアをうまく使える超並列ソフトウェアを作るということが必須である。

当時は、100K個のCPUコアを持つスパコンは無く、このような多数のノードを管理するインフラストラクチャは自分で開発することが必要であった。また、多数のノードを扱えるパフォーマンスモニタ、ツールなども存在せず、自分で開発を行った。

2006年11月のTop500リストでは、世界全体では27台のBG/Lスパコンが動作している。これだけ多数のスパコンセンターがBG/Lを選んだということは、高性能のスパコンを作るには、電力効率の高い簡単なCPUコアを多数並べるのが効率的であり、コスト的にも最適であるというBG/Lの考え方が正しいことを証明している。

BG/Lで始まったこの設計方針はスパコンの作り方の画期的な転換点となった。まさに、Blue Gene/Lは時代を変えたTest of Timeのスパコンのマシンである。

Blue Gene/Lの後継

そしてBG/Lの成功を裏付けるもう1つの証拠は、後継としてBlue Gene/P、Blue Gene/Qスパコンが開発されたことである。

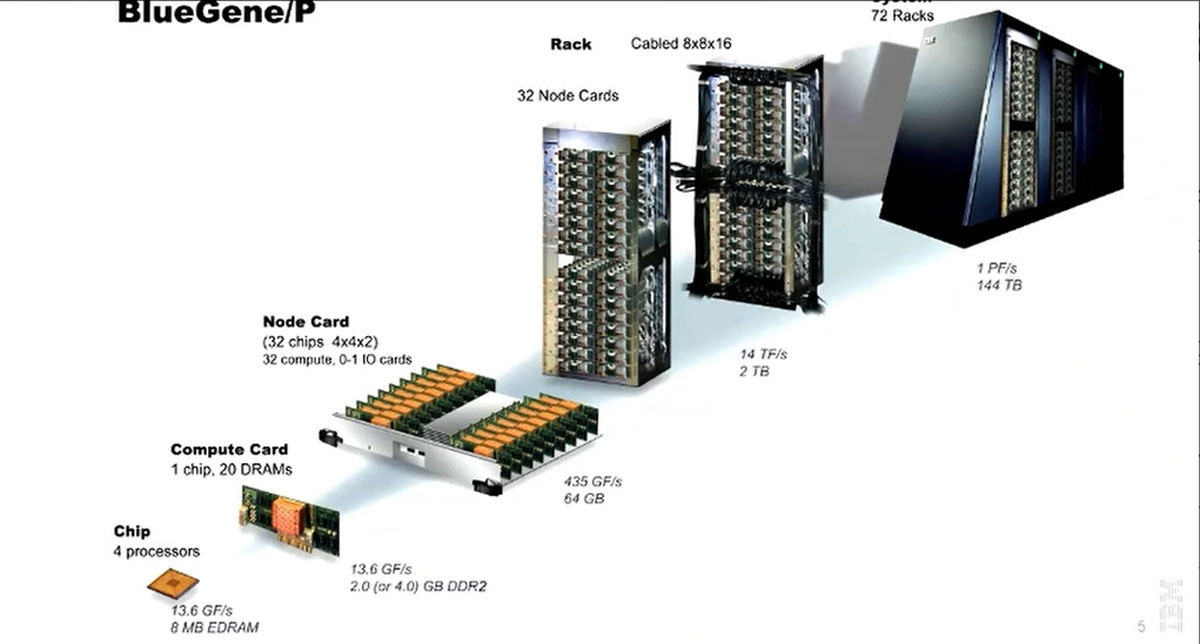

BG/Pは半導体のテクノロジの進歩を利用して1チップに4コアを集積し、キャッシュのeDRAMの容量も倍増した。これにより、Compute Cardの演算性能は13.6GFlopsとなった。しかし、次の図に見られるように、Compute Card以降の実装はBG/Lとほぼ同じであり、Node Cardは435GFlops、ラックは14TFlopsで、72ラックのシステムのピーク性能は1PFlopsであった。

-

BG/Lの後継のBlue Gene/P。Compute Cardのピーク性能が13.6GFlopsに上がり、メモリは2倍の2GBに増加した。そして、72ラックのシステムの演算性能は1PFlops、メモリ量は144TBとなった

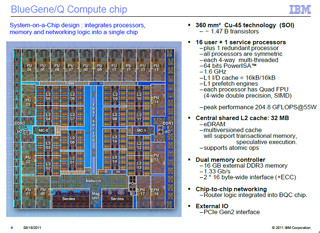

その後のBlue Geneスパコンは、2012年6月にTop500の1位となったローレンスリバモア国立研究所に設置されたSequoiaシステムである。このスパコンはBlue Gene/Qと名付けられている。初代のBG/Lから、約10年が経っており、使用した半導体テクノロジはIBMの45nmプロセスのCu-45である。これまでは半導体チップ内の配線はAl(アルミ)であったが、Cu-45は電気抵抗がアルミより低く配線を細くできる銅配線を使った。

そして、次のチップ写真に見られるように、18個のCPUコアとチップの中央に32MBのeDRAMのキャッシュを搭載している。18個のCPUコアの内、16個だけを演算用に使用し、1個のCPUコアは不良救済用の冗長コア、もう1個のコアはOSやネットワークの通信などを担当するサービスプロセサとして使用している。

また、チップ間のネットワークはBG/Lと同じトーラスであるが、BG/Lでは3次元のトーラスであったが、BG/Qでは5次元トーラスとなり、ネットワーク構成の自由度が改善されている。

BG/Qの1チップSoCは16個のCPUを持ち、演算性能は204.8GFlopsに向上し、消費電力は55Wとなった。

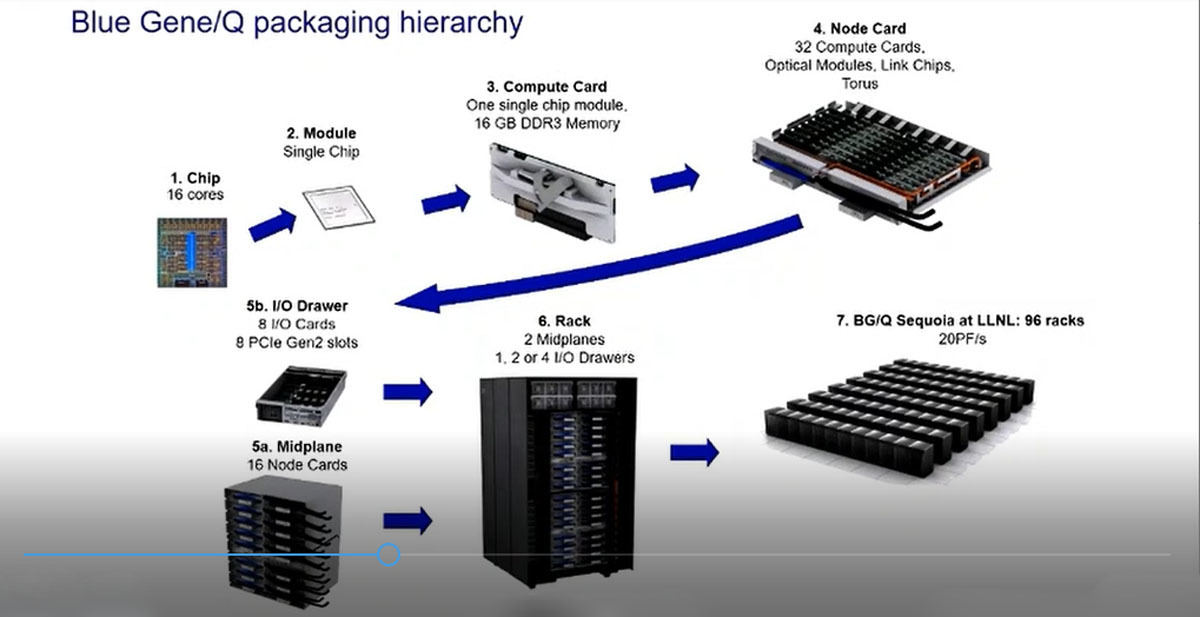

BG/Qのシステム階層を次の図に示す。第一階層のチップが16コアとなったので、第2階層のModule、第3階層のCompute Cardは1チップ搭載となり、第4階層のNode Cardが32枚のCompute Cardを搭載している。第5階層は、16枚のNode Cardを収容するMidplaneと8枚のI/Oカードを収容するI/O Drawerの2種のコンポーネントがある。

そして、第6階層がラックで、ラックは2つのMidplaneを収容し、最大4つのI/O Drawerも収容する。

BG/Q Sequoiaスパコンは、このラックを96ラック使い、1,572,864コアを搭載する。ピーク演算性能は20PFlops、LINPACK性能は16,324.8TFlopsでTop500の1位となった。

-

BG/Qのシステム階層。45nmプロセスを使い、1チップに16個のComputeコアを搭載し、これを1個搭載したCompute Cardを作り、Node Cardには32枚のCompute Cardを搭載する。そして、Midplaneに16枚のNode Cardを収容し、ラックには2つのMidplaneを搭載する。BG/Q Sequoiaシステムは96ラックで、20PFlopsの演算性能を持つ

そして、BG/Qでは熱密度が高いため水冷となった。Node Cardの写真の右下に見える2本のパイプは冷却水の給排水パイプである。

BG/Lの開発は、低電力のCPUコアを多数並べた新規な設計で、このような超並列の設計でスパコンが作れるのかという懸念があったが、結果として、低コストで高性能のスパコンを実現し、多くのスパコンセンターで使われた。という点で、Test of Timeに合格した設計であった。