ベルギーimecは、12月7日~11日に米国カリフォルニア州サンフランシスコで開催された「電子デバイス国際会議(2019 International Electron Devices Meeting:2019 IEDM)」にて招待講演4件、一般講演26件の合計30件もの発表を行い、ムーアの法則にしたがって1nmを目指した半導体微細化分野での存在感をアピール。うち2件の最先端デバイス研究をプレスリリースとして発表した。

2nmフォークシートデバイスのシミュレーション結果

imecは、かねてよりサブ3nmのポストGAA(ゲートオールアラウンド)デバイスとして、食事に用いられるフォークの形をしたフォークシートデバイスをアイデア段階で提案してきたが、今回のIEDMでは、TCADを用いた標準セルシミュレーション結果をはじめて発表した。

その結果、GAAデバイスと比較して、フォークシートデバイスは、n型デバイスとp型デバイスの間隔が縮小することにより性能が10%向上し、セル面積が20%削減できることを検証したという。

imecは、サブ3nmのデバイス構造が固まったことで、いよいよフォークシートCMOSデバイス製作に取り掛かることになるが、従来のGAA製作プロセスフローにわずかな工程を追加するだけで実現可能としている。

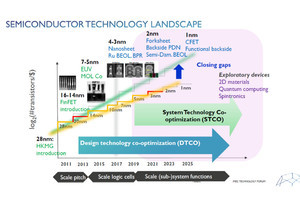

imecの3次元ハイブリッド微細化担当プログラムマネージャーのJulien Ryckaert氏は「半導体業界の微細化は、プレーナーからFinFET、そして垂直に積層したナノシート(やナノワイヤ)に移行しつつある。フォークシートは、ナノシートの延長線上にある、無理なく移行できる微細構造である。FinFET、ナノシートともn型とp型の分離距離が長く、微細化に支障をきたしていた。フォークシートデバイスは、究極のロジック用CMOSデバイスといえるだろう」と述べている。

2D材料の微細トランジスタで高い性能を実証

またimecは、2次元(2D)材料MoS2をチャネル部分に使用して微細化されたトランジスタを試作。2D材料に対して過去に報告されたものの中でも最高クラスのデバイス性能を実証したとIEDMで報告した。今後のトランジスタスケーリングのための2D材料の可能性を確認し、高性能ロジックとメモリアプリケーションの両方にメリットがあることを明らかにしたと説明している。

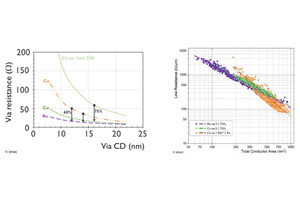

2D材料であるMoS2は、ほぼ原子の厚さと原子の精度で安定した形で成長できる。imecは、材料を単層(0.6nm)の厚みで合成し、コンタクトとチャネル長をそれぞれ13nmと30nmに縮小したデバイスを製作して検証を行った結果、微細化されたゲート酸化膜の厚さと高誘電率絶縁膜とを組み合わせ形で、これまでに報告されていた素子の中でも最高クラスのデバイス性能を実現したという。

試作されたデバイスのチャネル長は30nmで、コンタクトピッチは50nm未満。50nmのSiO2ゲート絶縁膜で250μA/μmのオン電流が実証された。バックゲート構成の4nm HfO2で、~100μA/μmのオン電流と80mV/decの優れたSSmin(VD=50mVの場合)が実証されたほか、デバイスのパフォーマンスは、コンタクト長のスケーリングの影響を受けないことを前提に、TCADシミュレーションに沿って、キャリアがコンタクト金属のエッジから直接チャネルに注入されることが確認されたという。

なお、imecのExploratory and Quantum ComputingディレクターであるIuliana Radu氏は、「Siトランジスタに比べると微細化のサイズはまだ一桁ほど離れているものの、2D材料を用いたMOSFETデバイスを将来のロジックおよびメモリアプリケーションに有望な性能を発揮する領域にまで持って来ることができた」と述べているほか、「ゲート酸化物の厚さのさらなる削減、二重ゲートアーキテクチャの実装、チャネルおよびインタフェースの欠陥のさらなる削減など、今後体系的にプロセスや構造の改善を図っていく。2D材料を使用した超小型デバイスで優れたパフォーマンスを実証できたので、今後300mmファブでの量産を目指して研究を続ける」としており、実用化に向けた取り組みを推進していくことを明らかにしている。