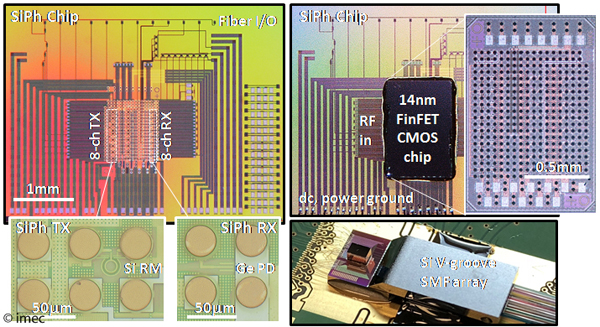

ベルギーimecは、Semicon Westに併せて開催した「imec Technology Forum USA 2018」において、FinFET CMOSロジック集積回路とシリコン・フォトニクスを混成して集積することで低消費電力と高帯域幅を両立させた光トランシーバを発表した。

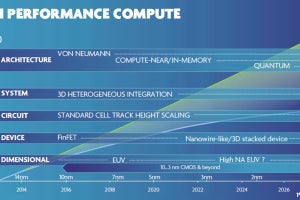

動的電力消費が230fJ/bitで、フットプリントが0.025mm2と小型かつ低消費電力な40Gbps非ゼロ復帰(non-return-to-zero:NRZ)の光トランシーバで、imecでは次世代高性能コンピュータに必要な超高密度、マルチTbpsオプティカルI/Oを実現するための重要な第一歩となると説明している。

データセンタスイッチや高性能コンピューティング(HPC)のノードにおけるI/O帯域幅は、さらなる広帯域の実現が求められており、今回の研究は、そうしたニーズへの対応を可能とすることを目的としたもの。具体的には、差動FinFETドライバとシリコンフォトニクス・リング共振器を同時最適設計することで、40GbpsのNRZで154fJ/ビットの動的消費電力を実現したとする。

また、受信機には、Geを用いた導波路型フォトダイオードで動作するように最適化されたFinFETトランスインピーダンスアンプ(TIA)を搭載。75fJ/ビットの消費電力かつ約-10dBmの推定感度で40Gbps NRZの光検出が可能である。

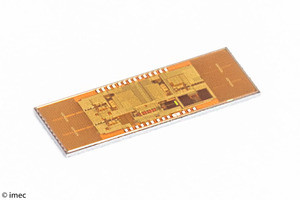

データ送受信については、2dBのリンクマージンを持つスタンダードシングルモードファイバ(SMF)上の1330nm波長でのループバック実験で実証されたほか、熱制御機能を統合した4×40Gbps、0.1mm2波長分割多重(WDM)トランスミッタも試作。ファイバあたり100Gbpsを超す帯域幅のスケーリングが可能であることを確認したという。

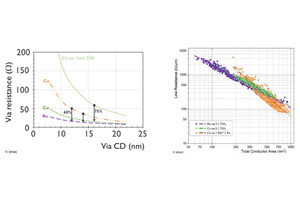

なお、今回発表されたハイブリッドFinFET-シリコンフォトニクス・プラットフォームは、14nm FinFET CMOSロジック回路と、高密度・低容量のCuマイクロバンプを用いた独自の300mmシリコンフォトニクス技術を活用して開発されたという。