5月下旬にベルギーで開催された「imec Technology Forum Belgium 2018」においてimecの半導体技術およびシステム開発担当EVPのAn Steegen氏がimecの半導体微細化プロセスや次世代半導体デバイスに関する今後の研究方針を語った(図1)。

Steegen氏は、今後のデータ取扱量の天文学的な増加から話を始め、PCによるインターネット時代には年間取扱データ量がギガバイト単位ものが、モバイル・ソーシャルメディア・クラウド時代にはエクサバイト単位へと増加し、AI・ビッグデータ時代となる現代はゼタバイト単位となってきていることを指摘。このような大量のデータ処理のためには、従来以上の高性能コンピュータが必要で、そのための半導体デバイスやこれを実現するためのプロセスが求められることを強調した。

これからのコンピュータに必要な技術

現在のコンピュータ製品は、消費電力(W)とシステム性能(演算回数/秒)により、3種類に大別される(図3)。1つ目は消費電力は大きいがシステム性能が高いデータセンター向け高性能コンピュータ。ここでは、単位電力当たりに性能向上が求められている。2つ目は、消費電力やシステム性能が中程度のモバイルコンピューティング機器。ここでは単位リーク電流当たりのシステム性能が求められている。3つ目は、消費電力は最小だが、システム性能も低いIoT端末機器で、可能な限りの超低消費電力が求められている。

それぞれの仕様に応じた半導体ロジックデバイスが求められており(図4)、高性能用やモバイル用では、従来の65~14nm CMOSが現在は10nm、将来は3nmの実現が見込まれており、さらにその先の微細化要求も根強くある。IoT用も従来の130~28nm バルクCMOSや28~22 FDSOIから今後は14nm バルクCMOSや12nm FDSOIへと置き換わっていくことが求められている。

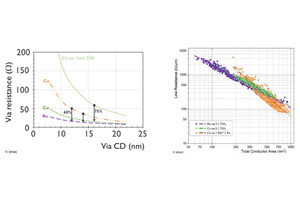

また、2018年、半導体のプロセスはついに10nmの壁を越え、7nm時代に突入しようとしている。imecでは、2020年代後半に迎えるであろう1.5nm時代に対応する高性能コンピューティングの実現のために、次のような研究を行っているという。

プロセスの微細化

- 7nmからEUVリソグラフィを採用

- 3nm以降は、EUVの高NA化で対処する可能性がある

- 250W高出力光源に対する耐性がある透過率95%のペリクル膜は開発済み

- 5nmを切るあたりから微細化に伴って、回路パターンにランダムに発生するマイクロブリッジ欠陥が顕在化してきたが、これについては、レジスト材料とプロセスとマスクおよび計測の同時最適化で解決するめどを立てている。

デバイスの構造

- 現在のFinFET構造を3nmあたりからナノワイヤ(あるいは幅広のナノシート)を用いた3次元積層ゲートオールアラウンド(GAA)構造へと進化させ、ソースドレイン間のリーク電流を完全に抑止させるとともにゲート制御性を完璧にする

- 微細化によるデバイス特性劣化を防ぐため、使われているすべての材料を見直し、新材料に置き換える

-

図6 高性能トランジスタ実現のための材料変更。配線材料をWからCoやRuに替えてコンタクト抵抗低減(左)、トランジスタのスペーサ材料をSiNからSiCOに替えてk値を下げてキャパシタンス低減(中)、チャネル材料をSiからGeに替えてキャリア移動度向上(右)。

回路設計・その他

- プロセス技術の助けも借りて、標準セルスタック高を縮小して、セル面積を比例縮小していく

- システムに関しては、異種のデバイスを同一基板上に集積する

- コンピュータ・アーキテクチャに関しては、従来のフォンノイマン型での改善を基本とし、HDDなどの外部記憶装置からデータをいちいち呼び出さないインメモリ(あるいはニアメモリ)コンピューティング化を図る、さらに将来にむけ量子コンピュータを開発している

新型メモリの開発動向

imecでは、既存のタイプのメモリの微細化・高性能化と並行して、あらゆる種類の次世代メモリの開発も行っている。現在は、NANDとDRAMの間に位置するストレージクラスメモリの開発に注目が集まっているが、図9は、その例として示されたimecが開発を進めている3次元縦型積層FeRAM。SRAMのセル面積のさらなる微細化やSRAM代替の不揮発性メモリの研究も行っているという。

-

図8 アクセス時間(秒)を縦軸、メモリ容量(ビット)を横軸にとって、さまざまな半導体メモリを位置付けたもの(STT-MRAMはSpin-Transfer-Torque Magnetic RAMの略。SOT-MRAMはSpin-Orbit-Torque Magnetix RAMの略。SGTはSurrounding Gate Transistorの略。ReRAMはResistive RAMの略)

-

図9 3次元ストレージクラスメモリの例としてのFeRAM。左がデバイス構造断面の透過電子顕微鏡写真、右が電流-電圧特性

-

図10 新型キャッシュメモリの例としてのSTT-MRAM。左が積層ゲート部分の断面透過電子顕微鏡写真、右が仕様一覧(右)

-

図11 新型キャッシュメモリの例としてのSOT-MRAM。左が積層ゲート部分の断面透過電子顕微鏡写真、右が電気的特性

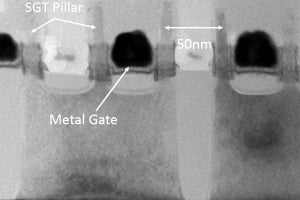

また、imecは、この講演に併せて、シンガポールUnisantisと共同で、SGT構造を採用した小面積SRAMセルを発表している。SGTは、フラッシュメモリの発明者として知られる舛岡富士夫氏が考案した縦型積層ゲートオールアラウンド(GAA)構造である。

-

図12 左がUnisantisとimecが共同開発したSGT搭載SRAMのセル面積の過去のISSCCで発表されてきたSRAMキャッシュセル面積の比較。右側は、Unisantisの考案したSGTの模式図(左側)と試作品の断面の透過顕微鏡写真(右側)。ただし、電気的測定結果は未発表である

加えて、imecでは、人工知能(AI)技術研究の一環として、神経細胞の働きを模したニューロネットワークアクセラレータの研究にも注力しているという(図13)。ASICやFPGA、GPU、RRAMなどを用いたさまざまな提案が行われており、すでに一部は商品化している。図13は、これまでに発表あるいは発売されているアクセラレータを消費電力と処理速度でプロットしたもので、imecでは30nm MRAMや5nm SRAMを用いることで市販のGPUに比べて消費電力を文字通り桁違いに小さくすることにめどを付けたとしている。

-

図13 いままで学会発表されたり、すでに市販されているさまざまなタイプ(ASIC, FPGA、GPU、およびRRAM)のニューラルネットワーク・アクセラレータの消費電力と処理速度による位置付け。黄色い星印はimecのデータ

このほか、Steegen氏のグループでは、3次元実装技術や高速光配線技術、顔認証や指紋認証のためのセンサ技術、次世代VR/ARディスプレイ技術など、広範囲の次世代デバイス・プロセス研究も手掛けているという。なお、imecは、コアCMOSデバイス・プロセス技術開発をSamsung Electronics、Intel、GLOBALFOUNDRIES、Micron Technology、Qualcomm、SK Hynix、SanDisk/Western Digital、TSMC、Huawei、ソニーセミコンダクタソリューションズ、東芝メモリと協業していることを明らかにしている。