ナノテク研究機関であるベルギーimecは、 650Vのノーマリオフ/エンハンスモード(e-mode)トランジスタを200mm GaN-on-Siliconウェハ上に試作することに成功したと発表した。

同トランジスタは、従来半導体技術比で、ダイナミックRon(オン抵抗)のバラつきが少なく(20%未満)、かつ高い性能と再現性、信頼性が得られたしており、imecでは要望があれば同社の200mm研究・試作ラインでの少量生産に応じるほか、パートナー企業への技術移転を行うとしている。今回の成果についてimecにてGaNデバイス開発を担当するDenis Percon氏は「この種のバラつきの少ない650VエンハンスモードGaNデバイスは、これまでにもパナソニックが小口径ウェハで試作したことがあったようだが、200mmウェハで試作したことはなかった。GaNデバイスを200mmウェハで生産することでコストを下げることは、同デバイスが市場に受け入れられるために重要なポイントになる」と述べている。

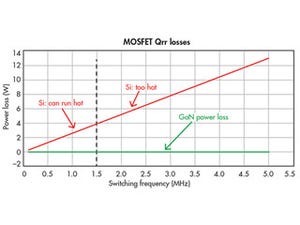

GaNデバイス技術は、従来のシリコン半導体に比べて耐圧が高く、オン抵抗が低い高速スイッチングパワーデバイスを提供てきるため、次世代のパワー半導体として期待されている。特に、今回試作されたGaN-on-Siデバイス技術はAuフリーであるため、シリコンウェハを取り扱うファブでプロセスを行うためのウェハハンドリングおよびコンタミネーション制御の要件と互換性があるため、導入障壁も低いとしている。

また、GaNデバイス構造で最も重要な構成要素は、AlGaN/GaN材料とSi基板の間の格子パラメータおよび熱膨張係数の差に対応するために必要とされるバッファ層であるが、新たなバッファ設計技術を開発することで、200mmウェハながら耐圧650Vのバッファを形成することができるようになったとしているほか、シリコン基板の厚さやドーピングの適切な選択によって、200mmでのGaN基板の歩留まりを競争力のあるレベルまで高めることができるようになったとしている。

|

|

|

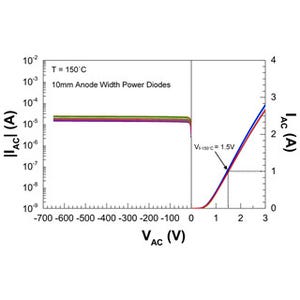

図3 imecの650VエンハンスモードGaN-on-Siトランジスタ(ゲート幅=36nm)の伝達特性 |

図4 imecの650 エンハンスメントモードGaN-on-Siデバイス(ゲート幅=36nm)のVgs=0Vの場合のリーク電流特性 |

さらに、洗浄プロセスと誘電体堆積条件の最適化などの改良も含めることで、25℃~150℃の全温度範囲にわたって650VまでダイナミックRonバラつき20%未満を実現したとimecでは説明している。

なお、imecのGaN技術のプログラムディレクターであるStefaan Decoutereは、「エンハンスト・モードのパワーデバイス・スイッチの次に、imecはパワー・スイッチング用の横型ショットキー・ダイオードも提供する計画だ。imecの独自のデバイスアーキテクチャに基づいて、このダイオードは低いターンオン電圧と低いリーク電流、最大650V -これらの特性を1度に達成するのが困難- を実現した」と述べている。