POWER9プロセサの概要

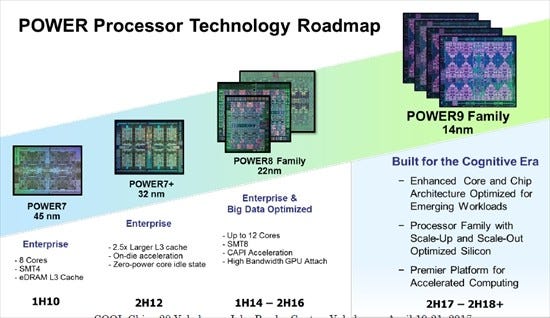

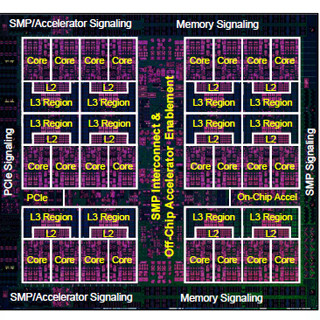

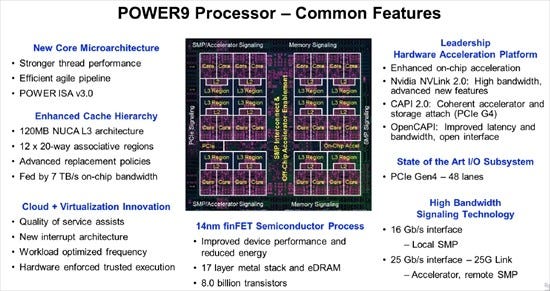

POWER9は、今年の後半に登場が予定されているIBMの次期プロセサである。14nmプロセスで作られ、コアやチップのアーキテクチャは将来のワークロードの処理も適するように作られており、認知コンピューティングの時代向けのプロセサであると銘打っている。POWER9はスケールアップ(大規模ノード)用のチップとスケールアウト(小規模ノードのクラスタ構成)用のチップが作られ、アクセラレータの接続機構も装備している。

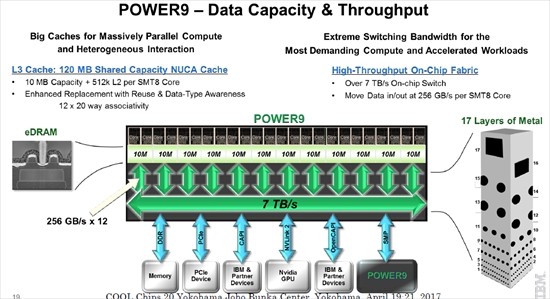

POWER9はPOWER IS 3.0準拠の命令アーキテクチャを持ち、スレッド性能を強化したマイクロアーキテクチャのプロセサである。14nm FinFETプロセスを使い、配線は17層で、8.0Bトランジスタを集積している。そして、24個のプロセサコアと120MiBという巨大なNUCA(Non Uniform Cache Architecture)のL3キャッシュを搭載している。

また、NVIDIAのNVLink2.0、CAPI 2.0、OpenCAPIというアクセラレータ接続用のインタフェースを備えている。POWER8もアクセラレータ接続用にCAPI(Coherent Accelerator Processor Interface)を備えていたが、POWER8では、この機能が大幅に強化されている。

|

|

POWER9プロセサは14nm FinFETプロセスで作られ、8.0Bトランジスタを集積する。24個のプロセサコアと120MiBのL3キャッシュを搭載する。新しい用途への拡張を可能にするNVLinkやOpenCAPIなどのアクセラレータインタフェースを装備している |

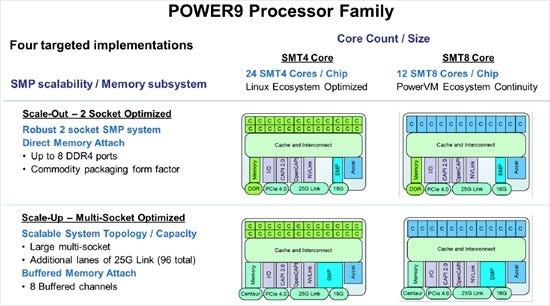

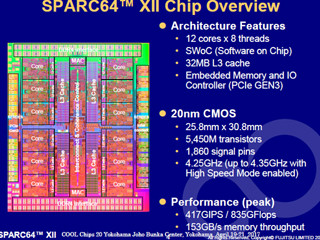

POWER9ファミリには、並列スレッド数が4のSMT4コアと、並列スレッド数が8のSMT8コアがあり、SMT4コアの場合は24コア、SMT8コアの場合は12コア搭載という仕様になっている。SMT4コアはLinux用であり、SMT8コアはPowerVM向けである。

しかし、どちらのコアを使ってもチップ全体での並列実行スレッド数は96スレッドで同じである。

さらに、POWER9プロセサには、2ソケット構成のスケールアウト用に最適化したバリエーションと96本の25Gbit/sリンクを使ってマルチソケットのシステムを作るスケールアップ型のバリエーションがある。スケールアウト型のチップは16枚のDDR4 DIMMを直結するようになっているが、スケールアップ型のチップはバッファチップを使ってDRAMを接続する構成になっており、スケールアウト型の2倍のメモリバンド幅と2倍の記憶容量を持たせることができる。

ということで、SMT4とSMT8それぞれにスケールアウト型とスケールアップ型があり、全体ではPOWER9チップには4種のバリエーションが存在することになる。

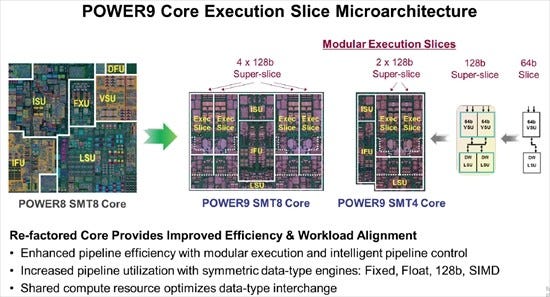

次の図の左端は、POWER8のSMT8コアのチップ写真である。POWER8の場合は8スレッドの実行資源は渾然一体に作られていたが、中央の写真に示すPOWER9のSMT8コアは4つのExecスライスと1つの命令処理部(ISUとIFU)で作られている。

そしてSMT4コアは2つのExecスライスと半分幅の命令処理部で作られており、POWER9の設計はモジュラーになっており、バリエーションが比較的容易に作れるようになっている。

|

|

POWER8ではSMTの8スレッドの実行資源は渾然一体に作られていたが、POWER9では64bitのスライス(2スレッド分)を2つ並べたスーパスライスを基本単位として、スーパスライスを2個使ってSMT4コア、スーパスライスを4個使ってSMT8コアを作っている |

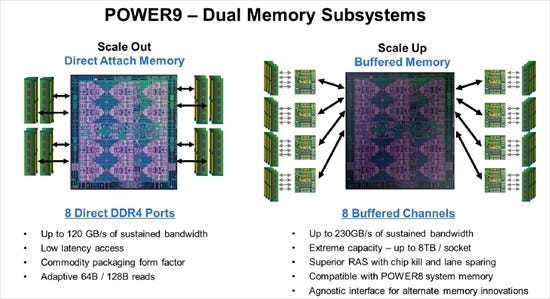

そして、左の図のように、スケールアウト型のチップでは16枚のDDR4 DIMMを直結するようになっており、メモリバンド幅は120GB/sとなる。また、DIMMを直結しているのでアクセス時間が短いという特徴がある。

一方、スケールアップ型のチップではバッファチップを経由して、全体では2倍のメモリを接続できるようになっている。このため、メモリバンド幅は230GB/sとなり、CPUチップあたりの最大メモリ容量も8TBに達する。また、バッファチップにはRAS機能が組み込まれており、DRAMチップが1個故障しても動作を続けられるChipKillや、メモリチャネルが1ビット故障すると代替のレーンに切り替えるレーンスペアなどの機能がサポートされる。

なお、スケールアップ型のメモリは、バッファチップと多数のDRAMチップを1枚の基板に搭載したIBMカスタムのサイズの大きいDIMMとなっている。

スケールアウト型で言えば、2コアあたりに20way 10MiBのL3キャッシュスライスが付いている。このL3キャッシュは、IBM得意のeDRAMで作られており、通常のSRAMで作るよりも密度が高い。

12個のL3キャッシュスライスを合わせると3.072TB/sというバンド幅になる。12個のスライスは1つのキャッシュとして動作するが、スライス間の距離が長いので、アクセスする場所によってアクセス時間が異なるNon Uniformなキャッシュとなる。そして、7TB/s以上のバンド幅を持つスイッチでL3キャッシュと、メモリ、PCIe、アクセラレータ用のインタフェース、他のPOWER9チップの接続インタフェースなどに接続している。

右側のポンチ絵は17層の配線を示すもので、1~5層は細い配線で配線密度を稼いでいるが、上層の配線は抵抗の低い太い配線で、電源線やクロック配線、長い信号線などに使われていると考えられる。