既報のとおりXilinxは2月21日(米国時間)、FPGAにアナログ機能を統合した「All Programmable RFSoC」を開発中であることを明らかにした。同発表に先駆け、同社はメディア向けに概要説明会を開催したので、その模様をお届けする。

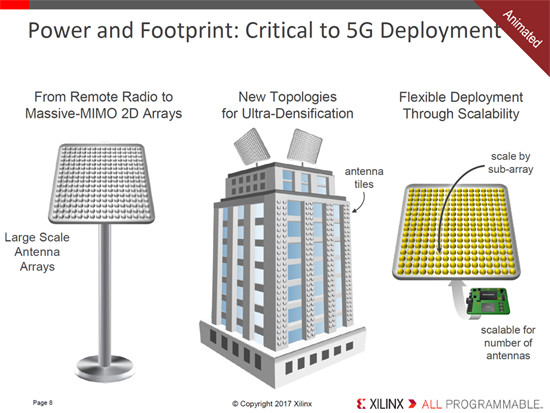

まず5Gの実用化に向けた動きについて簡単に振り返ってみると、基地局としては当初、4G/LTEではラジオ部とアンテナ部が分かれたシステムとなっていたが、この間に介在するI/O部で電力が散逸、大電力が必要となっていた。近年では、この2つを統合したアクティブアンテナとすることで、省電力化が図られつつあるが、これが5Gとなると、広帯域幅による大容量通信を実現する必要から、Massive MIMOを使用した大規模アンテナアレイを構築することが必要となる。大規模アンテナアレイとは言いつつも、その実用的なシステムサイズを考えると、ビルの看板などに取り付けられる程度の小型化を実現しつつ、スケーラビリティを確保し、ニーズに応じてアンテナアレイの数を増やして対応するといった形になる模様で、1システムあたりで考えると、省フットプリントかつ低消費電力を実現しなくてはいけないこととなる。

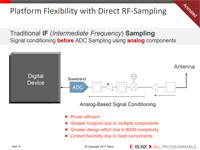

「5Gに向けたMassive MIMOには、低消費電力、フォームファクタの小型化、設計期間の短縮を可能とすることが必須の条件となる」と語るのは、Xilinx Director,Communications marketのHarpinder S Matharu氏。従来の4G/LTEでは、フロントエンドにAll Programmable SoC、この後段にJESD204準拠のインタフェースが挟まれ、トランシーバを経由してA/Dコンバータ(ADC)とD/Aコンバータ(DAC)と接続といった構成であっても、レシーバ/トランシーバの数は限られていたので問題なかったというが、トランシーバ/レシーバの数が圧倒的に増える5Gでは、I/O部で消費される電力が高くなり、低消費電力化のボトルネックとなっていた。

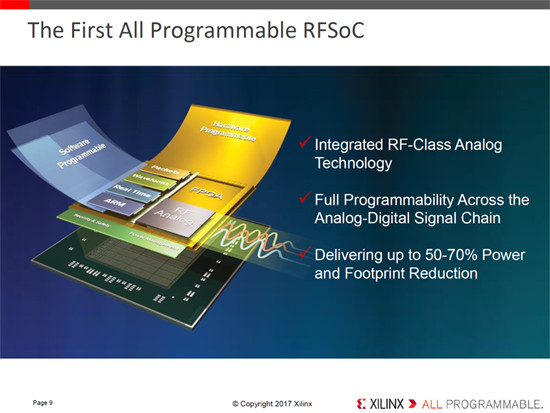

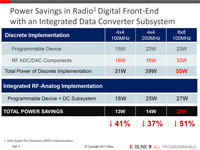

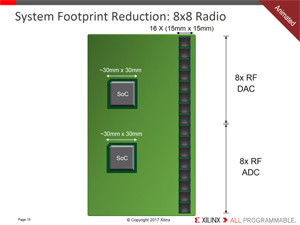

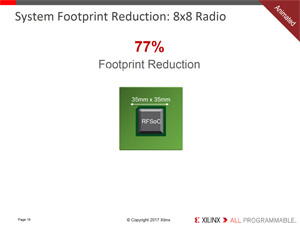

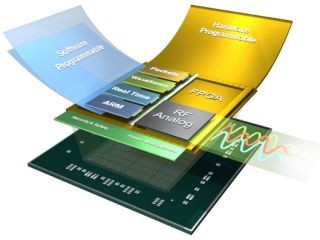

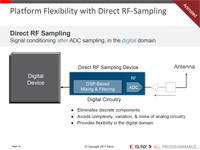

RFSoCでは、このI/O部をチップ内に統合。これによりI/O部での電力消費を無くすことができるようになったほか、プリント基板上に配置されるADCやDACといったディスクリートの数も減らせるので、フットプリントの削減も可能になるとのことで、従来ソリューションで8×8 100MHzの通信システムを構築した場合に比べてRFSoCでは消費電力が約51%減となる27W、プリント基板のサイズも約77%減と小型化を図ることができ、かつ層数そのものも減らせるようになるとする。

また、FPGAの利点を活かして、同じデザインながら周波数帯ごとにチューニングをすることで、それぞれの周波数に対応させることが可能になるため、設計の煩雑さも軽減できるという。

「理想的な状況は、複数の周波数において、うまく動くADC/DACを使えるというものだが、現実は難しい。しかし、RFSoCでは、互いに独立した最適な周波数を使うことができるようになる。つまり、どのようなデジタルデザインであれ、望ましい帯域に対応することが可能となる。実際の性能もシステムベンダと相談して決定した」(同)とするアナログ部の性能は、RFダイレクトサンプリング方式に対応できる最大4GSpsの12ビットADCと最大6.4Gbpsの14ビットDACとなっており、プログラマブル性も有しているとする。「今回はあくまで技術的な紹介であり、製品の話ではないが、実際のアンテナでも8×8を1単位としてスケーラビリティを持たせる形になるのではないか」(同)という。

|

|

|

|

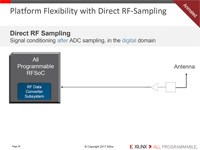

ダイレクトRFサンプリングによるプラットフォームの変遷。左がアナログコンポーネントを使用した従来の方法。中央がデジタルデバイスにDSPベースのミキサーやフィルタといったデジタル処理を組み合わせたもの、右がRFSoCを用いたもの。徐々にシンプル化が進んでいるのがわかる |

||

さらにXilinx VP,Platform Product MarketingのTim Eljavac氏は、「Xilinxでは2010年ころよりアナログ部分のパフォーマンスに注目して開発を進めてきた」と、開発の背景を説明しており、決してぽっと出のアイデアでアナログを統合しよう、と思ったわけではないことを強調。プロセスとしてもTSMCの16nm FinFET CMOSプロセスをアナログ部にも適用させることで実現したとのことで、挑戦的な技術を使っている、というわけでもないことを説明していた。

すでにテストチップならびに商用ボードに近い状態のものが動作するデモが存在しており、その動作状況も上々とのことで、気になるのは実際の製品展開のスケジュールだが、Tim氏は「2017年後半には詳細を発表できる」と説明しており、具体的なラインアップなどについては、その際に明らかにするということであった。

なお、日本法人ザイリンクスの代表取締役社長であるSam Rogan(サム・ローガン)氏は、「2020年に5Gのサービススタートと日本では言われているが、韓国メーカーなどを見ていると、2018年の平昌五輪で5Gのサービスをスタートさせようという動きもある。そうした意味では、先行者利益を得るためには、どうしても先んじて技術を開発していく必要がある。世界はすでに水面下で商用化に向けた動きを活発化させている。日本が掲げている2020年が世界で初めての5Gのサービス開始時期になる、という夢からは目覚めてもらいたい。今、世界に先んじて動かなければ、日本メーカーは有意なポジションを確保することに苦労することになる可能性が高い」と、Xilinxの日本および韓国担当バイスプレジデントとしての立場から見た、世界における5Gの実用化に向けた動きを述べており、RFSoCを日本メーカーに活用してもらうことで、競合よりも早い実用化に向けた手助けができれば、としていた。