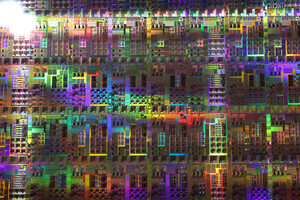

米ザイリンクスは21日(米国時間)、RFクラスのアナログテクノロジをザイリンクスの16nm All Programmable MPSoCに組み込んだ、5G無線向けのインテグレーションおよびアーキテクチャを発表した。

同社のAll Programmable RFSoCにより、ディスクリートのデータコンバータが不要になるため、5G Massive MIMOおよびミリ波無線バックホールアプリケーションの消費電力とフットプリントを、50~75%削減できるという。

大規模2Dアンテナアレイシステムは、5Gに要求されるスペクトル効率の向上とネットワークの高密度化の鍵を握ると見込まれている。また、メーカー各社は、5Gの商用展開のための厳しい要件を満たす新しい方法を探す必要性に迫られている。All Programmable SoC上に高性能なADC(アナログ-デジタルコンバータ)とDAC(デジタル-アナログコンバータ)が統合されたことで、無線バックホールユニットはチャネル密度を増加させながら、これまで達成不可能だった消費電力とフォーム ファクタの要件を満たすことができるようになった。また、RFSoCデバイスを使用するメーカーは、設計および開発サイクルを効率化することで、5Gの商用展開のスケジュールに合わせることが可能となる。

なお、16nmベースの一体型RFデータコンバータテクノロジの特長は以下の通り。

・ダイレクトRFサンプリングによるアナログ設計の簡素化、高精度化、小型化、低消費電力化

・最大4GSPS、多チャネル、デジタルダウンコンバージョンを行う12ビットADCを搭載

・最大6.4GSPS、多チャネル、デジタルアップコンバージョンを行う14ビットDACを搭載

スタンフォード大学電気工学科教授であるボリス ムルマン(Boris Murmann)氏は、「FinFETテクノロジへのシフトにより、高い集積度と改良されたアナログデバイス性能の特性が融合されます。その結果、デジタルベースのアナログ設計手法を使用して、最先端のアナログ/RFマクロを統合できるようになります」とコメントを寄せている。

ザイリンクスのFPGA開発およびシリコンテクノロジ担当コーポレートバイスプレジデントであるリアム メイデン(Liam Madden)氏は、「RF信号処理を内蔵するAll Programmable SoCを利用すれば、システムのアーキテクチャを劇的に変革できます。All Programmable RFSoCは、ザイリンクスの至上命題である継続的かつ革新的なシステムインテグレーションの一環でもあります。5G分野のお客様は、RFSoCの登場により、競合に対して差別化できる大規模なMassive MIMOおよびミリ波バックホールシステムを実質的に商用展開することが可能になります。ザイリンクスの新しいRFSoCアーキテクチャは、5G開発の緊急課題に対応するのにまさに絶好のタイミングで発表されました」と述べている。