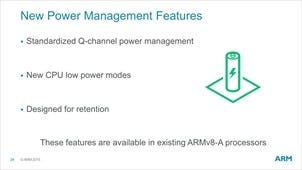

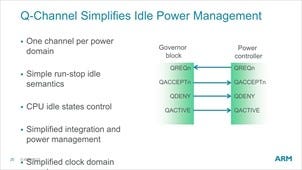

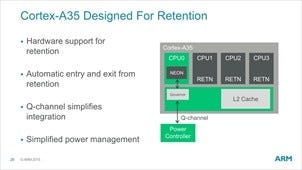

さて次が省電力関連である。Cortex-A35がCortex-A7と比べて省電力化を実現できた理由の大きな部分は、新しい省電力機構を搭載したことにある(Photo17)。まずQ-Channelであるが、これはAMBA/AHBのSideband(Ian Smythe氏)という形で実装される(Photo18)。

|

|

|

Photo17:これらの機構は既存の64bit ARMプロセッサにも搭載されているらしい |

Photo18:Sidebandの意味はこの場合、既存のAXI/AMBA AHBの信号線とは別に設けられるという事になる |

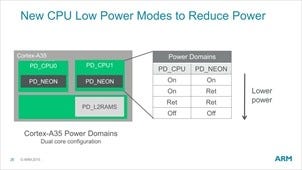

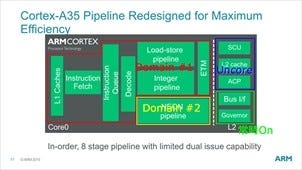

なにをやっているか、というとCPUの動作状態がQ-Channelを経由して外部のパワーコントローラに通知されており、ある程度以上アイドル状態が続いたと外部のパワーコントローラが判断すると、Q-Channelを経由してCPUに対して(この後説明する)リテンション状態に入るように指示する仕組みだ。これはパワードメインごとに用意されており、Cortex-A35の場合はNEONで1つ、NEON以外のCPUコアで1つという形になる。ちなみにPhoto05を見るとL2やSCU/ACPもコアの一部に見えるが、こちらは実装としてはコア外になるので、実際にはPhoto19の様になる。

|

|

Photo19:Bus I/FとGovernorはコアの一部であるが、ここの電源をカットすると復帰できなくなるので、ここは常時ONであり、その意味ではコア内にDomain \#1/\#2と常時ONの3つのドメインがあるといっても良いのかも知れない |

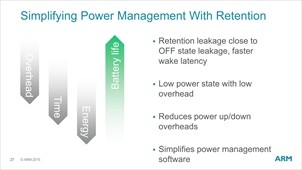

さてこの2つのパワードメインに対して新しく用意されたのがRetention Modeである。これは何かというと、復帰のために必要な最低限のプロセッサステートを保持しつつ、回路の電圧を落とすというもので、サスペンドとアイドルの中間に位置するものになる(Photo20)。

この結果として、電源完全カットに近い程度までリーク電流を減らしつつも、完全電源Offよりも迅速に復帰が可能になるという仕組みだ(Photo21)。このRetention Modeの制御を行うのが、先に説明したGovernorである(Photo22)。Governor(とRetentionで利用される保持領域)は原則常に電源ONで、Q-Channelからの指令を受けてコアに対しての電圧制御を行う事になる。

|

|

|

Photo21:実際にどのへんまで電圧を落とすのか、というのは利用するプロセスの種類によって変わってくるものと思われる |

Photo22:そもそもRetentionの入るのはCPUがアイドル状態にある時なので、Contextの保持などはそれほど必要ないというのが、電源管理を簡単にしている肝となる |

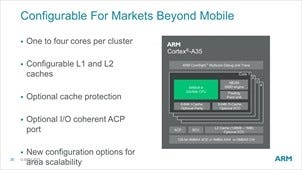

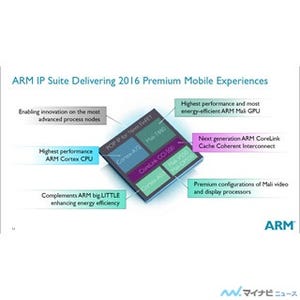

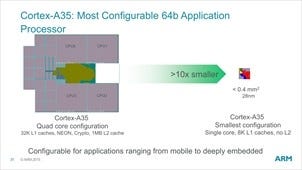

次がスケーラビリティの話。Cortex-A35は最大4コアまでの構成が可能である(Photo23)。ではbig.Littleは? というと、「任意の64bitのCortex-Aシリーズでbig.LITTLEを構成できる」(James Bruce氏)という話で、(意味があるかどうかは別にして)例えばCortex-A35とCortex-A53でも、Cortex-A35とCortex-A72でもbig.LITTLEを構成できるとの話だった。

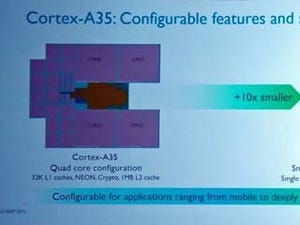

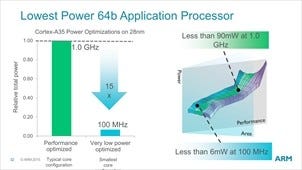

またCortex-A35自身がバリュー向けのスマートフォンのみならずウェアラブルまでターゲットにしていることもあり、最小構成だと28nmで0.4平方mmまでエリアサイズを縮小できるとしている(Photo24)。実はこの2つは、同じ28nmといっても利用するプロセスも最適化方法も異なっており、左は性能優先で恐らく28nm HPMあたり、右はエリアサイズ優先で28nmのLPないしULPを使ったものの様だ。このあたりは当然ターゲットとする周波数にも関係してくる。それがPhoto25で、LPなりULPを使うと動作周波数は100MHz程度まで落ちる代わりに6mW未満で動作し、逆にHPMあたりを利用すると90mWで1GHzを実現できることになる。

|

|

|

Photo24:「これはイメージであって、比率は正しくない」(Ian Smythe氏) |

Photo25:もちろん1GHzの場合はマルチコア構成が想定され、L2などもあるから全体としては数百mWのオーダーになるのだろうが |

この6mW未満、というのはちょっと高速なMCUと同レベルであり、またエリアサイズが0.4平方mmというのもやや古めのプロセスを利用したMCU並である。要するにCortex-A35は(2014年に発表したCortex-M7とあわせて)MCUとMPUの性能面での境目を無くすという同社の遠大なストラテジーを担う、結構重要な製品と考える事もできる。

搭載製品が投入されるのは早ければ2016年末であり、当初はスマートフォンのエントリーモデル向けであろう。ただし2016年中には既存のCortex-A5/A7ベースの組み込み向けコントローラの代替としてこれを採用したSoCがラインアップされはじめるだろう。いよいよ組み込みそのものが64bitに本格シフトの準備が整いはじめた訳だ。