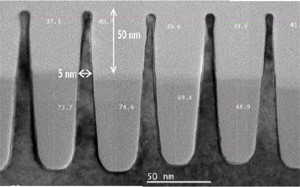

次は、デバイス構造を従来のプレーナ―(平面)構造から3次元(立体)構造に変更することによってデバイス性能を向上させる方法である。MOSFET微細化を達成する上で一番大きな問題点は、いかにしてMOSFETスイッチオフ時のソース・ドレイン間の漏れ電流を抑制するかにある。Intelが世界で初めて22nmからMPU製品に導入したFinFET構造はゲートが上部と左右の3面からチャネルを取り囲んでいるので、ゲートの支配力が増して、リークを強力に制御できる。TSMCやSamsungはあとを追って16/14nmからFinFETを採用している。FinFETでは3面にゲートがあるのでIntelはTri-gateと呼んでいる。FinFETの性能をさらに上げるには、フィン幅を狭めると共にフィンの高さをさらに高めればよい(いわゆる「トールフィン(tall fin)」)(図6)。しかし、このようにするとフィンが倒れやすく、製造がますます困難になっている。チャネル移動度を高めて、トランジスタを高速化するために、フィンの構成材料をシリコンよりもキャリア移動度が大きなゲルマニウム(Ge)やIII-V属化合物に替える方向が鮮明になっている。

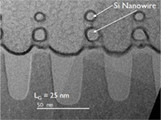

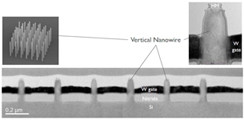

FinFETの先にあるのがシリコンナノワイヤFETである(図7)。チャネルを全方向からゲートで覆ってしまう、いわゆるall around gate構造を採って、リーク電流を完全に制御する。その先にあるのが、ナノワイヤを垂直に並べて高密度化する垂直ナノワイヤFET(図8)、さらにその先にナノワイヤFETの3次元積層化が出現するだろう(図9)。ここでは、3次元NANDフラッシュのプロセス技術が役立つかもしれない。

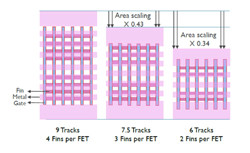

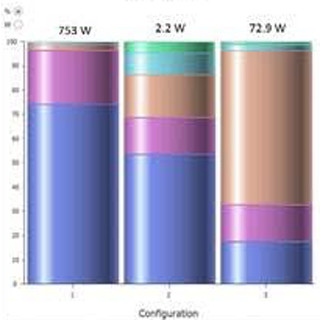

サーバのパフォーマンス向上の3番目の手段は、セルライブラリーのトラック数の削減による専有面積のスケーリングだ(図10)。従来の9トラック(FinFETあたりのフィン数4)を7.5トラック(フィン数3)さらには6トラック(フィン数2)と減少させるにつれて図10に示したように面積を大幅に縮小する。

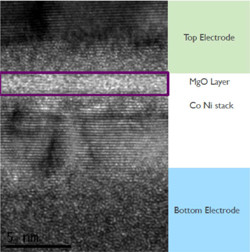

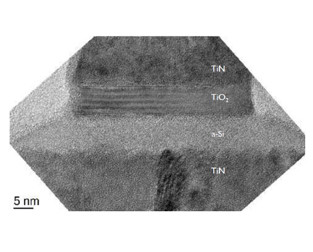

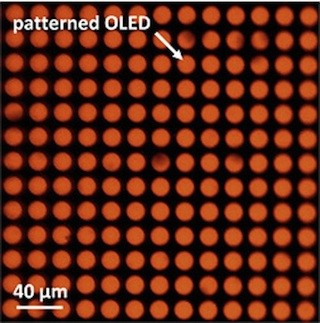

imecでは、新しいスイッチングデバイスとして、トンネルFETやスピン波デバイスなども試作検討している。次世代メモリデバイスとしては、STT-MRAM(図11)やRRAM(図12)などを試作検討している。これらのスマートデバイスを基にして、imecは独自のIoTを提案し実現していく。