先日、Cortex-A72の内部構造の詳細レポートをお届けしたが、そもそもこれは同社が4月22・23日にロンドンで開催したTech Dayで明らかにされたものである。そのTech DayではCortex-A72以外にも多くの情報が明らかにされたので、順次レポートしてゆきたい。まずは「Cortex-M7」に関してである。

Cortex-M7は昨年9月に発表されたハイエンドMCU向けコアであり、11月のARM TechConでもう少し詳細が明らかにされたが、今回はもう一段細かな話である。

まずPhoto01はIntroductionとして、Cortex-M系列全体としての話であるが、2014年までで108億個もの出荷個数を誇り、2014年だけで44億個、トータルでは280以上のライセンス出荷数となっており、製品種類は3500を超えるとする。さてそのCortex-Mのシリーズ製品、性能という順番で並べたのは以前示したこちらのプレゼンテーションだが、機能/特徴という観点でまとめたのがこちら(Photo02)。左から右に、どんどん機能や特徴が追加されていった形になる。余談になるが、Cortex-Mシリーズは最初のCortex-M3を中心に、低消費電力版と高性能版を交互に追加してきた形になっており、してみると次は再び低消費電力版ということになるのだが、果たしてどうなるやら。

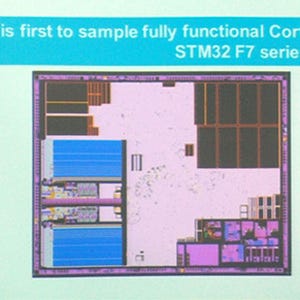

さてそのCortex-M7、現在公開されているメーカーはこの4社であるが(Photo03)、非公開のメーカーを合わせるとすでに10社がライセンスを受けているとする。そのCortex-M7の特徴を簡単にまとめたのがこちら(Photo04)。特にDSP性能に最適化を行ったとしているが、それがどういう形の最適化を施したかは後で出てくる。

|

|

|

Photo03:ちなみに会場では「SPANSIONではなくCypressだろ?」という突っ込みもあったが、返事は「今はそうだが、ライセンスを提供したときにはSPANSIONだった」そうで |

Photo04:性能とか機能だけを見ていればアプリケーションプロセッサと言われても不思議ではないが、にも関わらずCortex-M7をMCUに留めておく最大の理由がThumb2のみのサポートというあたりだろう |

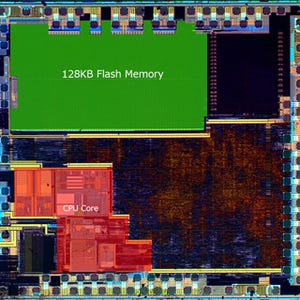

また、新機能として追加された特徴その1はこちら(Photo05)。L1とかTCMの実装は前回の記事でも紹介したが、AXI4が標準装備になったのは、すでにAMBAではCortex-M7が要求する帯域(特にデータ帯域)が満たせない事を物語っている。特徴その2がこちら(Photo06)で、遂に倍精度浮動小数点演算をサポートしたほか、デバッグ用のETMがデータトレース機能を持つv4になり、さらに機能安全用途向けにECCの強化やLockStepのサポート、それとOn-line BISTの実装が行われている。次のスライド(Photo07)は以前のこちらと差が無いので説明は割愛する。