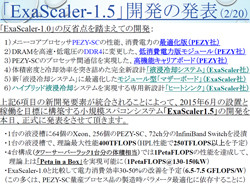

2015年2月20日に大阪で開催されたPCクラスタコンソーシアムの「PCクラスタワークショップin大阪2015」において、PEZY Computingの齊藤元章社長が特別講演を行い、その中で、睡蓮スパコンに使用した「ExaScaler 1(ES1)」を大幅に改良した「ExaScaler 1.5(ES1.5)」の開発を発表した。このES1.5ではPEZY-SCチップを使用するが、実装密度を4倍に改善し、性能/電力も30-50%向上する。また、PEZY-SC2チップからPEZY-SC3、4チップを含むロードマップを発表した。次世代のPEZY-SC2チップに関しては、すでに開発を開始しているという。

ExaScaler 1ではフッ化炭素による浸漬液冷を実現したが、液相だけを使う単純な構成しか間に合わせることが出来なかった。また、空冷を前提としたSuperMicro社のサーバブレードを流用したため、体積が大きく液冷のメリットを十分活かしきれていない。また、マザーボードの設計から、PCI Express経由のPEZY-SC間の通信が利用できないなどの問題があった。また、PEZY-SCはDDR4 DRAMに対応した設計となっているが、DDR4 DRAMの入手が困難で、DDR3を使わざるを得なかった。

PEZY-SCチップもES(製品に使用しても良いが、本来は技術評価用の試作品)しか間に合わず、本来のターゲットに比べて、動作クロックがかなり遅めのチップしか使用できなかった。そのため、電源電圧を下げるなどのGFlops/Wの改善が出来なかった。

また、チューニング期間が短く、十分なコードの最適化が出来なかったなどの問題がES1では残ってしまっていたという。

これらの問題を解決するES1.5の開発について、齊藤社長は、特別講演の中で明らかにした。

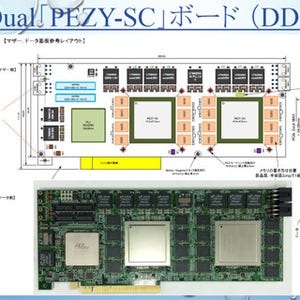

ES1.5ではプロセスパラメータを最適化して本来の目標性能となる量産チップを使い、電源電圧を下げるなどの省電力手法を使って性能/消費電力を最適化する。そして、DRAMもDDR3からDDR4に変更してメモリバンド幅の改善と低電力化を行う。また、既製品のマザーボードではなく、PEZY-SC間にPCI Express経由の通信ができるボード(正確には、マザーボードをキャリアボードに搭載する構造)を開発する。

体積密度と冷却効率を突き詰めた完全新設計の液冷システムを開発し、この液冷システムに最適化したボードを開発し、気液2相を使うハイブリッド液浸冷却を実現するヒートシンクを開発する。

そして、2015年6月には、これらの改善を行ったES1.5を設置して稼働させるという意欲的なスケジュールを提示した。これが実現できると、1台の液浸槽に64個のXeonと256個のPEZY-SC、そして、36ポートのInfiniBandスイッチ2台を収容できる。そして、4台の液浸槽で、倍精度浮動小数点演算のピーク性能で1.6PFlops、LINPACK性能で1PFlops(消費電力130-150kW)のシステムが作れる。液浸槽4台の体積は、ほぼ19インチラック1本と同じであり、Peta in a Boxのシステムが実現できることになる。この開発が順調に進めば、2015年7月にドイツのフランクフルトで開催されるISC2015で展示を行う予定であるという。

「ESLiC-32」と呼ぶES1.5の新冷却槽は、16個のモジュールを収容する構造になっている。各モジュールは14cm角で長さが約80cmの角柱である。このモジュールには4枚のキャリアボードが入っており、それぞれのボードにXeon1個とPEZY-SC4個が搭載されている。従って、全体ではXeon64個、PEZY-SC256個が新液浸槽に収容できる。

そして、ボードの上部にはInfiniBandのNetwork Interfaceカードと電源が配置されている。さらに、4×4のモジュールの外側に36ポートのInfiniBandスイッチが搭載されている。そして、モジュールの角にある角柱のパイプから冷媒のフッ化炭素を供給する。

ES1の液浸槽はXeon16個、PEZY-SC64個収容であったでので、新液浸槽にはXeon、PEZY-SCともに4倍の密度で詰め込まれている。

またこのシステムはXeonを4個搭載するキャリアボード、XeonとGPU、あるいはXeon Phiを2個搭載するキャリアボードの開発も行っているという。

そして、その先の2016年にはPEZY-SC2がある。

|

|

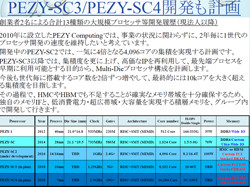

PEZY-SC2は14-16nmのFinFETテクノロジを使い4096コアを集積し、1GHzクロックで動作させる。メモリはUltraMemoryの3D積層DRAMを使用し、4TB/sのバンド幅を実現する |

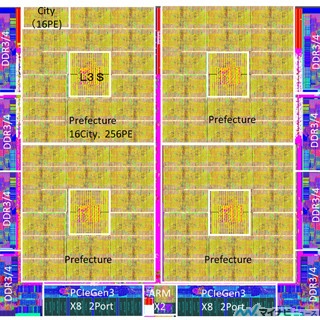

PEZY-SC2は、14-16nmのFinFETテクノロジを使い、4096コアを集積して1GHzクロックで動作させる。これにより、ピーク演算性能は単精度では16.4TFlops、倍精度では8.2TFlopsとなる。そして、圧巻なのが、UltraMemoryの開発する3D積層DRAMを使うメモリシステムで、このメモリは1個当たり500GB/sのバンド幅を持ち、これを8個接続することで4TB/sのメモリバンド幅を実現する計画である。8.2TFlopsの演算性能(F)で4TB/sのメモリバンド幅(B)であるので、B/F比は0.49となる。各社のCPUやGPUでは0.2程度のB/F比というのが一般的で、PEZY-SC2はメモリバンド幅が律速となる計算には大きな威力を発揮しそうである。

そして、齊藤社長は、PEZY-SC2に続く、PEZY-SC3、PEZY-SC4についても開発を計画していることを発表した。

PEZY-SC3は10nmプロセスを使い、8192コアを集積し、2018年の完成、PEZY-SC4は7nmプロセスを使い、16384コアを集積し、2020年完成というロードマップである。

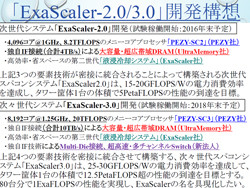

そして、これらのプロセサを使うES2.0、3.0の開発も構想している。ES2.0では前述のSC2.0とUltraMemoryの500GB/sのメモリに第2世代の液浸冷却技術を組み合わせ、15-20GFlops/Wの電力効率を実現する。ラック1本あたりの性能は5PFlopsである。

ES3.0では、8192コアでピーク20TFlopsのSC3に10TB/sのバンド幅のメモリを接続する。冷却システムも第3世代に進化させ、チップ間接続インタフェースや、高速、多チャネルのスイッチを独自開発してシステム性能を上げる。

ES3.0では25-30GFlops/Wを目指し、ラック1本あたりの性能は12.5PFlopsとなる。このラック80本で、1ExaFlopsとなり、社名のExaScalerを具現化したいという。

|

|

SC2を使うES2.0、SC3を使うES3.0の開発も視野に入っている。ES2.0では15-20GFlops/W、ES3.0では25-30GFlops/Wを目指す。ES3.0では1ラックで12.5PFlops、80ラックでExaScalerの社名を具現化するExa Flopsの実現を目指す |

なお、インタコネクトのボトルネックを解消するチップ間の接続インタフェースや、高速、多ポートのスイッチの技術開発には、新会社を設立する予定であるという。