回路最適化などにより性能向上を実現

さて、発表会における説明はこの程度だったが、このあともう少し細かい話を聞けたのでご紹介したい。まずはCPUコアについてである(Photo20)。

まずCortex-A72のマイクロアーキテクチャであるが、既存のCortex-A57のEnhancementであり、例えば現在の3way Superscalerを4wayにしたりはしていないとの事である。ではどうやって性能を改善したかというと、専ら細かなEnhancementであり、RTLレベルでの回路最適化を相当施した模様だ。この結果として、エリアサイズを同じプロセスノードで比較すると、若干ではあるがCortex-A57より小さくなるそうだ。そんなわけで、アーキテクチャそのものもARM v8-Aで、しかも(Cortex-A9→Cortex-A15の様な)アーキテクチャそのものの拡張は一切行われていないとの事。またパイプライン長などの詳細は現時点では公開できないとの事だった。

次に、Cortex-A72のPrimary TargetはMobileであるが、長期的にはサーバやその他の用途もターゲットにおいているとの事。この「その他の用途」には自動車向けも含まれる。実のところ既存のCortex-A57/Cortex-A53も自動車の、特にADAS向けの用途を考慮しており、長期的にはこれらに対してISO26262のCertificationをARM自身が取得して顧客に提供するという話はすでに明らかにされていたが、Cortex-A72も同様にISO26262のCertificationを取得するという事だ。ただ面白いのは、同じ自動車向けでもCortex-RやCortex-Mに関してはISO26262 ASIL-Dをターゲットにしているのに対し、64bit Cortex-AはASIL-Bがターゲットということだ。最終的な操作系の制御を握るECU向けにはASIL-Dが必要だが、ADASはASIL-Bで十分という判断との話だった。

話をコアそのものに戻すと、今回POP IPの形で提供されるのはCortex-A72と、big.LITTLE構成となるCortex-A53のみで、Cortex-A57については見送りになるようだ。引き続きCortex-A57そのものは提供され続けるが、新規デザインについてはCortex-A72で、ということになるようだ。つまり、Cortex-A57がミッドレンジクラスのコアになる、という訳ではないらしい。逆に言えば将来的にミッドレンジのコアが出るのか、については「それはミッドレンジのマーケットがどの位早く64bitに移行するのか次第」ということで、それが遅くなるようであれば当面はCortex-A53とbig.LITTLE構成で十分という判断らしい。その場合、例えばCortex-A72×2とCortex-A53×4のbig.LITTLEといった構成をミッドレンジに持ってくるといったデザイン上のフレキシビリティもあるという話であった。

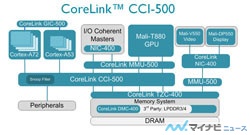

次にインターコネクトについて。ARMはCortex-A53/A57の発表時にCCN-500というインターコネクトを発表しているが、これはRing Bus構造でスケーラビリティはあるものの、消費電力などの観点ではMobileに適さないとされていた。そこでMobile向けに開発されたのが今回のCCI-500(Photo21)である。

|

|

Photo21:この図はこちらの記事から抜粋したもの |

最大の違いは内部構造がCrossbarベースということで、さらにSnoop Filterを内蔵することで無駄なトラフィックの削減を行い、インターコネクトの実効転送効率向上と消費電力削減を両立させたという話だった。ただ当然ながらスケーラビリティはCCN-500シリーズほどなく、2つのCPU ClusterとGPUを接続することにフォーカスしているとの話であった。そのSnoop Filteringであるが、これを行う際には内部にキャッシュをもち、ここを参照しながらそのSnoopを送り出すか否か判断することになる。なので、キャッシュの持ち方次第で回路規模とレイテンシが決まる(トレードオフの関係になる)が、今回はまだそうした具体的な話は公開できないとの事だった。

なおインターコネクトそのものはそんなわけで変わるが、割り込み管理のI/O MMUのMMU-500などはCCN-500シリーズと同じものがそのまま利用できるとの事だった。

なおCCI-500に関してはPOPの提供予定はないとのことである。