テクトロニクス社は9月25日、100Gbps通信システムの電気分野向け製品とソフトウェアのラインナップを拡充すると発表した。

「LE320型」は2つの差動チャネルと9つのタップを装備したリニアイコライザで、BERTScopeレシーバテストシステムの一部として最高32Gbpsのデータレートをサポートする。また、マルチチャネルBERT「PPG/PED」シリーズの新オプションは、最高32Gbpsのデータレートにおけるストレス信号の出力と出力調整が行える。さらに、40Gbpsのエラーディテクタモデルも発表。加えて、サンプリングオシロスコープ「DSA8300型」の新オプション「CEI-VSR」は、CEI-28G-VSR規格で必要になるコンプライアンステストの自動化を実現するという。

設計テーマが、半導体からトランシーバ/システムへと移行しており、4×25Gテストが重要になっている。現在は、25~28Gbpsの4レーンを使用した、最高100Gbpsの革新的なネットワークエレメントを製作などが行われている。このような高い周波数の信号は、たとえ短い距離であっても、プリント基板上で伝送することで設計上の問題が発生する。「LE320型」は、汎用性の高い出力信号コンディショニングの設定、チューナブル入力イコライゼーション機能を装備しており、25~28Gbpsで動作する4つの電気チャネルテストのための光システムを構築することができるため、パターンジェネレータ/エラーディテクタ製品「PPG/PED」のマルチチャネル機能を補完する。サンプリングオシロスコープのOpt. CEI-VSRは、効率的で一貫性のあるコンプライアンステストをサポートするため、製造へのスムーズな移行が可能になる。

10Gbps以上のシステムを開発する場合、Rx入力の前段にイコライザを、またはトランスミッタのTx出力でプリエンファシスモジュールが必要される。高速化し、12Gbps以上でこの要件を満たそうとすると、優れた信号コンディショニング機能を持つ限られた製品しか選択肢がなくなる。「LE320型」は、CEI-28G-VSRなどの100G通信規格で規定される高確度エラーレートテストで使用される8~32Gbpsのデータレート、9タップ設計の信号コンディショニングをサポート。革新的なリモートヘッド設計により、「LE320型」はテストシステムのケーブル長を短くすることができ、25~28Gbpsで顕著となる信号劣化の問題を防ぐことができる。「LE320型」は、Hittite社のカスタムマイクロ波半導体をベースとして部品数を削減しており、価格を従来製品や手法の1/3とした他、スマートフォンと大きく変わらないサイズの計測器グレードのパッケージで革新的な性能と汎用性を実現している。

「LE320型」はプログラマブルイコライゼーションによって規格固有のイコライゼーションを設定することができ、閉じたアイ信号のBER解析が行える。低データレートを扱うユーザーには「LE160型」を用意しており、40G-KR4、14Gbps Fibre Channel、16Gbps PCI Express 4.0などのアプリケーションの20Gbpsまでのシステムに対応できる。

一方、マルチレーン、高速データレートの規格により、マルチチャネルのビットエラーレート計測器のニーズが高まっている。複数の高速パラレルレーンへの移行により、ストレスレシーバテスト、4チャネルのエンドツーエンドBERテスト、クロストークテストが中心となっている。同社の「PPG/PED」シリーズ、マルチレーンBERTは、拡張されたジッタストレス機能、新しい出力調整による柔軟性、高速のエラー検出機能により、これらの規格要件に対して十分に対応できる。

ジッタインサーションの拡張レンジオプションにはOpt. HFJITが含まれており、BUJ、RJ、SJ、および大振幅/低周波のPJも新しいOpt. LFJITの一部として提供される。さらに、Opt. ADJには、32Gbpsマルチチャネルパターンジェネレータアプリケーションで必要になる、高速の立上り/立下り時間を持った出力調整機能と低固有ジッタが追加される。新製品のエラーディテクタ「PED4000」シリーズは、最高40Gbpsのデータレートをサポートし、1または2チャネル構成により、データレートのマージンテストの強化が可能となっている。

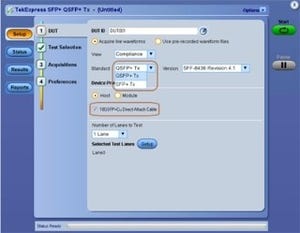

高速で信頼性の高いCEI-28G-VSRコンプライアンステストOIF CEI(Optical Interworking Forum Common Electrical Interface)3.0のIA(Implementation Agreement)では、OIF規格をベースとしたデバイスのテストとリミットを規定している。CEI-28G-VSRはこれらの規格の1つであり、プラグ式光トランシーバの非常に短い電気チャネルに使用される。これらの電気インタフェースはシステムのBER(Bit Error Rate)ターゲットに適合できることが重要であり、厳しいテストとデバッグサイクルを受けなければならない。

従来、CEI-28G-VSRの全てのコンプライアンステストを実行し、ジッタやノイズに関係する問題を特定することは難しい作業であり、労力を要するものだった。シリアルデータリンク解析ソフトウェア「80SJNB」と統合することにより、別の計測器または測定セットアップに移動することなく、詳細なデバッグとタイミング問題の原因解析が行える。

サンプリングオシロスコープ「DSA8300型」とOpt. CEI-VSRを使用することで、5分以内でコンプライアンステストが実行できるため、手作業によるテストに比べて約95%もの時間短縮が可能になる。さらに、Opt. CEI-VSRを使用することで、CEI-28G-VSRのHost-to-Moduleインタフェース仕様で規定されるCTLEピーキングの最適値を求めることができる。数多くのフィルタから最適なCTLEフィルタが選択され、測定で使用される。同機能がないと、時間をかけて手作業で最適なCTLEの値を求めなければならず、作業生産性が低下するとしている。