謎のP1271.9

さて、記者説明会の話は大体この程度だったが、その後でもう少し詳細な話をBismuth氏に伺う事が出来たので、ちょっとご紹介したい。

まず製品ラインアップ。現在は(Photo12にちょろっと出てきた)「ABAX2P1」という製品のみが提供される。このABAX2P1には3種類のSpeed Gradeがあり、一番低いABAX2P1-1が内部クロック(同社のDatasheetによればSpacetime Clock)は1.425GHz、その上のABAX2P1-2が1.667GHz、ハイエンドのABAX2P1-3が2GHz駆動になる。これにあわせてトランシーバとかDDR3 Hard IPのData Rateなども変わってきており、例えばABAX2P1-1はトランシーバは最大10.3GHzだしDDR3は1600MHzまでになっている。

これに続くものは? というと、内部的にはロードマップはあるが、まだ公開できないとの事。例えばより高速な製品も、逆にもう少し遅い製品も出すことは可能だが、それは顧客のニーズによるという話だった。これはラインアップとしてもそうで、例えば現在はWired Networkに特化した構成になっているが、他の用途向けの製品は「考慮中ではある」とするものの、具体的な話は無かった。これはIPに関してもそうで、例えばPhoto19を見るとPCIeは用意されている(PCIe Gen3はもうちょっと後になるとの事。またGen4は将来、だそうだ)が、SRIOは無い。これを尋ねると「Wireless Network向けにはSRIOは必要だが、まだWireless向けのSolutionは手がけてないから」という話だった。まだ同社は社員数130名余のベンチャー規模だから、今はWired Network一本に絞って製品展開をしており、あれこれ手をだすゆとりはない、という事なのだろう。

4月1日追記:当初ABAX203という製品名をご紹介しましたが、Tabulaによればこれは社内番号で、製品名としては「ABAX2P1」になるとの事。TabulaがCustomer Portalで公開していたドキュメントの中にABAX203の名前があったため、これをそのまま使いましたが、これはうっかり社内番号がまだドキュメントに残ったままだった、との事で現在ドキュメントの改定中との事です。以上お詫びして訂正いたします。

次にマーケット。例えば同じIntelの22nmプロセスを使って製造されるAchronixとの差別化として「Achronixの製品にはコメントできないが、我々のアドバンテージは単にDeviceを提供するだけでなく、Solutionを提供するところにある」とした。

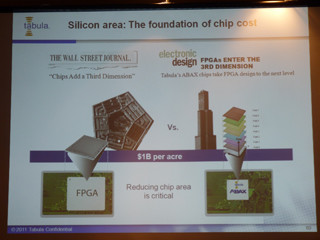

また逆にXilinxやAlteraのハイエンドFPGAに対するアドバンテージとしては、Photo07の4つのボトルネックのうち「Line TerminationとかExternal Bandwidthは他社でも同等のSolutionが用意されるかもしれないが、DatapathのBottleneckとかInternal Memory Bandwidthの解消は同社の最大のアドバンテージである」とした。従来型のFPGAは配線数が膨大になってしまうのが問題だし、Silicon Interposerを使ったMulti-Chipタイプの場合は、さらにボトルネックの問題が大きくなるとし、「Silicon Interposerは素晴らしいアイディアだしチップ間の接続は非常に早いが、Interconnectの問題解消にはならない。むしろ配線長が増える事で遅くなる」とした。もっとも「一応確認させてほしいが、Tabulaは将来もMulti-Chip Solutionを出さないという認識でいいのか?」と聞いたところ「ノーコメント」という返事が返ってきたあたりは、メリットはメリットとして認識しているということだろう。

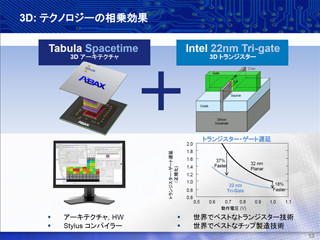

またAlteraがIntelの14nmプロセスを使う事に絡んで、次世代製品のプロセスをどうするのか? と確認したところ「将来製品についてはコメントできないが、当社は常に最先端のプロセスを使った製品をリリースすることをコミットしている。実際Spacetime Technologyは、先端プロセスを使う事でよりFold数やメモリ量を増やしたり速度そのものを上げる事が出来るので、これは単純にメリットになるからだ」という答えであった。

ちなみにこの22nmプロセスだが、Clock Gatingに関して言えばStylusの側でSub-Cycleの単位でこれを完全に制御しているとか。ただPower Gatingに関しては実装しているかどうか判らない、との事だった。

ところで気になるのはその22nmでの開発過程。「論理設計はTabula、製造がIntelというのは判るが、では物理設計はどちらが担当したのか」とお聞きしたところ「両社の共同作業だ」という返事であった。少なくともIntelが物理設計レベルで受託をした訳ではなく、TabulaのエンジニアがIntelと一緒に物理設計を行ったそうである。

さて、最大の謎がその22nmプロセスの正体。Intelはご存知の通り、High-Speed Logic向けのP1270と、SoC向けのP1271の2種類の22nmプロセスを提供している。で、ABAX2はどちらのプロセスを使っているのかを確認したところ、氏はそこまでご存知ないということだったが、後追いの形でTabura本社からTabula Japanを経由して「1271.9というマイクロプロセッサとSOCの混合プロセスで両者の利点を兼ね備えています」という返答を戴いた。さて、これは何だろう? ということでインテル(日本法人)に問い合わせたところ「基本的にP12xxというプロセス名は、社内のコードであり、対外的には22nm世代のプロセスとお答えしております」という返事を戴いた。

ということで以下筆者の想像。Tabulaの回答にもあるように、P1271そのものではないようだ。実際、ABAX2の核にあたる部分は明らかにHigh-Speed Logicの塊であり、これはP1270の方が適している。ただABAX2はそれ以外に64個の14.1Gbps Transceiver、最大2.133GHzで動くDDR3 Controller×4、最大64個のEthernet MAC、576本のParallel I/Oなどの周辺回路を搭載している。特に576本のParallel I/Oは最大1.8Vの駆動が可能になっており、これはP1271でないと難しい。そこで2種類のプロセスを組み合わせる形で製造を行ったのだと思うが、これにP1271.9という型番が付いているのは、すでにP1271.1~P1271.8といった派生型があって9番目の意味なのか、もしくはこれが22nm台では最後の派生型であり、14nmのP1272の1つ手前なのでP1271.9と名づけられたのか。筆者的には2つ目の方がありそうな気はする。Achronixにも同じ質問を投げかけたいところであるが、とりあえず単純にP1271を使って製造、という訳ではない事が判ったのは収穫と言えそうだ。