Alteraは9月5日(米国時間)、同社の次世代FPGAとなる20nmプロセス製品に搭載される技術の概要を公開した。20nmプロセスFPGAはこれまでのFPGAより3つの点が進化すると同社Senior Vice President,CTOのMisha Burich氏は語る。その3つの進化点とはどういったものであるのかについて同氏に詳細を聞く機会をいただいたので、その概要をお伝えしたい。

消費電力を抑制しつつシステム性能を向上させるためには

同社が3つの進化を20nm FPGAで果たしたという背景には、システムの高性能化、高機能化に伴う消費電力の増大がある。例えばIntelは消費電力と熱の問題から動作クロックの上昇ではなく、マルチコアへと舵を切った。また、スーパーコンピュータは電力を気にしないでハイエンドのCPUを複数台搭載したサーバをつないでいけば、いまでも次世代の目標であるエクサスケールを実現できるだろう。しかし、その実現には発電所がどれだけ必要になるか、というレベルになってしまう。

また、もう1つの課題として、汎用のプロセッサのみで処理をするよりも動画などの決まった処理については専用のコアなどを用意して演算させた方がワット当たりの処理性能は向上するが、すべてのプロセッサにすべてのDSPやハードマクロを搭載すると使わない機能などがでてきて、コスト高や基板面積の無駄につながる。

そこで単一デバイスへマイクロプロセッサ、DSP、FPGA、ASSP、ASICを統合することで、必要に応じてそれらの機能を使い分ける、いわゆる「シリコン・コンバージェンス」という考え方が登場してくる。「Alteraは20nm FPGAでそれらを統合するために究極のシステム統合プラットフォームとも言える"ミックスド・システム・ファブリック"の提供を行うことで、これらをユーザーが柔軟に活用することが可能になるようにする準備がある」と同氏は語る。

|

|

|

「シリコン・コンバージェンス」に対してAlteraのスタンスとしては、FPGAの利点を生かし、さまざまな機能を統合することで、求める機器に最適化された高い性能を柔軟に提供することを目指すというものとなっている |

|

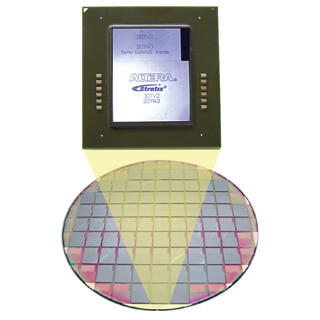

そして、それを実現するための技術的な3つの進化が今回発表されたものとなる。第1の技術とされるのが「ヘテロジニアス3D IC」だ。同社の20nm FPGAには2つのアプローチがあるという。1つはモノリシックのFPGAのダイ上にDSPやARMコアなどを搭載する従来的な手法。もう1つが3D IC技術というわけだ。同社は2012年3月にTSMCのCoWoS(Chip on Wafer on Substrate)統合プロセスを採用した、ヘテロジニアス3D ICのテスト用デバイスを共同で開発したことを発表している。

CoWoSはサブストレート基板上FPGAやASIC、メモリなどを搭載して、それを1チップ化する技術だ。TSVなどを使ってダイとダイをスタックする完全な3Dではなく、いわゆる2.5D ICの部類に入る技術であるが、「製造コストと信頼性を考えると、TSVを使うような3D ICではダイ間で生じる熱をどう逃がしてやるかが問題になっており、数年先には解決できると思うが、現在の選択肢にはなりえなかった」(同)ということである。これにより組み合わせられるのは、FPGA、HardCopy ASICといった同社の製品のほか、他社のASICやメモリ、光モジュールが予定されており、同社がシステムベンダからそうしたデバイスを受け取り1チップ化して提供するとのことで、「これによりシステムの消費電力の低減、基板面積の削減、およびシステムコストの削減が可能になるほか、チップ間の距離が縮まることによる性能の向上も図れるようになる」(同)とする。

各種のデバイスが1チップ化されるので、色々と開発が面倒なことになるような気がするが、その点に関しては「FPGAベンダである我々は、すでにFPGAを中核デバイスとして、さまざまな機能を内部に取り込んできた。ARMコアの搭載も実現しており、こうした次世代ヘテロジニアス3D ICであっても、開発ユーザーが使用するソフトウェア上では例えばFPGA内部のメモリとチップ上にある外部のメモリは同一のものとして扱うことができるようにするなどの工夫を施している」と説明する。

超高速トランシーバによる通信と次世代の可変精度を実現したDSP

2つ目の技術となるのが「次世代トランシーバ技術」だ。20nm FPGAではバックプレーン(装置内の各基板間通信)での28Gbpsでの通信ならびにチップ間およびチップ-光モジュール間の40Gbps通信を実現することが可能となるほか、将来(2014-16年ころが目安)的には56Gbpsのサポートも計画されているという。

|

|

トランシーバの速度が向上することで、データのやり取りできる量が増えることとなるが、高速化はノイズとの戦いであり、ノイズをいかに抑えるかの技術が重要になるが、その点が同社の技術力の発揮するところでもあるという |

そして3つ目の技術となるのが「次世代の可変精度DSPブロック」への対応だ。これにより単精度のIEEE 754の浮動小数点演算性能は従来の28nmプロセス品の5倍以上となる5TFlops超となるという。

鍵を握るソフトウェア

これら3つの技術のほか、ソフトウェアもこの進化に併せて強化されることとなる。ただし、同社のソフトウェア名である「Quartus II」に変更はないという。「もはやQuartus IIはブランドであり、それを変えるつもりはない。それは過去の製品にも対応し続けるという我々の意思の表れでもある」と同氏はその意義を語る。

では20nm FPGA向けには3つのコンポーネント「Qsys」「OpenCL」「DSP Builder」の強化が図られる。これは2013年に発表されるバージョン13より対応が図られる予定。「これらの機能強化に加え、大規模化したシステムのコンパイラタイムをどれだけ早くできるかもポイントとなる。目標としては、現状のシステム開発時のコンパイラタイムと同じであり、その実現に向けた開発を進めている」と、大規模FPGAの開発におけるボトルネックの解消を図っていくことを強調する。

また、OpenCLへの対応はHPC分野への対応を図るためだが、同社ではスーパーコンピュータが活用されるような学術分野ではなく、銀行や証券、オイル/ガス田の採掘といったビジネス分野でのHPC活用に対応することがメインになるという。「FPGAを搭載したPCI Express Gen3のボードを挿すだけで、ネットワークの処理からプロセッサでのデータ処理、ユーザーへの返信までマイクロ秒の単位で実現することができるようになる。また、サーバに搭載されているインタフェース用FPGAをコプロセッサ的に活用する試みもすでにサーバベンダ各社で始められている。GPUコンピューティング(GPGPU)がHPC分野のアクセラレータとして注目されているが、FPGAはGPUに比べて1/10の電力対性能比を実現できる。これは同じ電力であれば10倍の性能をだせることを意味する。そのためのOpenCLのサポートであり、ネットワークとの連携が必要な分野は使い勝手の高いFPGAにシフトしていくだろう」と、Top500のようなスーパーコンピュータのランキングには入らないようなシステムで、その存在感を増していくとの将来予測を同氏は語っている。

|

|

ハードウェアの機能が複雑化すればするほどソフトウェアの重要性は増してくるという。特にQsysについては、システムの開発規模が肥大化するにつれ、その重要性は増してくるとしている。また、HPC分野への適用としてのOpenCLへの対応などは今後、重要な意義を持つようになるとする |

プロセスの微細化によりチップサイズを変えずにトランジスタ数が向上してきたことがFPGAをシステムの周辺の処理からシステムの中心へと移そうとしていたのが28nmプロセスの世代であったが、20nmプロセスではその適用分野が民生分野からHPC分野まで、さらに拡大されようとしている。