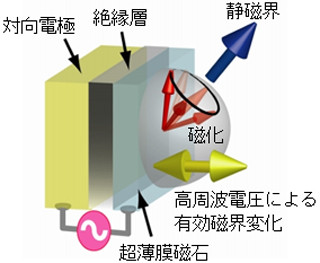

産業技術総合研究所(産総研)は5月8日、次世代半導体材料として期待される「p型ゲルマニウム」の中へ、室温で磁性体のスピン情報を入力することに成功したと発表した(画像1)。

成果は、産総研ナノスピントロニクス研究センター 半導体スピントロニクスチームの揖場聡研究員、Ron Jansen(ロン・ヤンセン)招聘研究員、齋藤秀和研究チーム長らの研究グループによるもの。研究の詳細な内容は、5月9日付けで科学誌「Applied Physics Express」オンライン版に掲載された。

|

|

画像1。半導体ゲルマニウムへのスピン入力を観測するための素子の模式図。スピン入力のための電極は鉄と酸化マグネシウムから構成される。鉄からゲルマニウムへ電流を流すことによって、ゲルマニウムに鉄のスピン情報が入力される |

IT機器は待機中も電力を消費しており、省電力化のためにはその削減が必要である。現在のコンピュータの主要半導体メモリは電源を切ると情報が失われてしまう揮発性メモリで構成され、待機中も電源を切れない。そのため、電源を切っても情報が失われない不揮発性メモリで既存メモリを置き換えることができれば消費電力を大幅に抑制可能だ。

「トンネル磁気抵抗(TMR)素子」は、ナノオーダーの極薄絶縁体の上下を磁性体でサンドイッチした構造を持つ。上下の磁性体の磁化の向きが平行の場合と反平行の場合で素子の電気抵抗が大きく変化するという特徴があり、磁気ヘッドや磁気ランダムアクセスメモリにはこの素子が利用されている。

そのTMR素子を既存の半導体トランジスタと組み合わせるハイブリッドタイプのメモリデバイスは、実用間近の段階まできている状況だ。しかし、このような手法には、素子構造の複雑さや、デバイス性能がTMR素子によって決まるといった問題が存在する。そのため、高速で低消費電力を単一素子で実現できる革新的な「スピントランジスタ」の実現が期待されているというわけだ。

スピントランジスタとは、電子の持つスピンを演算に利用するトランジスタのことである。電源を切っても情報を失わないため、コンピュータの超省電力化に大きく貢献できると考えられているデバイスだ。

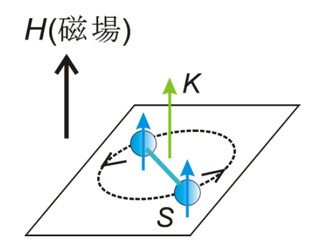

ちなみにスピントランジスタの実現のためには、(1)強磁性ソース電極から半導体チャネルへのスピン情報入力、(2)ゲート電界印加による半導体チャネル内でのスピン操作・演算、(3)強磁性ドレイン電極によるスピン操作・演算結果の検出技術を室温で確立する必要がある(画像2)。

そんな中で高速動作できる次世代トランジスタ材料として注目されているのが、シリコンの4倍を超えるキャリア移動度を持つ「p型ゲルマニウム」だ。キャリア移動度とは、半導体中における電気伝導の担い手であるキャリア(電荷または正孔)の移動速度を表す指数のことだ。この値が大きいほど、素子の高速動作が可能になる。

またp型とは、n型と共に2種類ある半導体のこと。p型はプラスの電荷を持つ正孔が、n型はマイナスの電荷を持つ電子がそれぞれ電気伝導の担い手(キャリア)となる仕組みだ。

従って、p型ゲルマニウムに磁性体からのスピン情報を効率良く入力できれば、グリーンIT(地球環境に配慮した省電力素子やシステムのための技術のこと)化に向けての大きな推進力となることが期待される。

しかし、これまでスピン情報の入力は摂氏マイナス180℃以下の極低温に限られていた。このため、スピントランジスタの実用化を目指すにあたり、室温でスピン入力できる技術が求められているというわけだ。

産総研は、これまでスピン機能を動作原理とする新型素子や不揮発性メモリデバイス、いわゆるスピントロニクス(固体中の電子の電荷とスピンの両方を利用する工学及び研究分野)デバイスの開発に取り組んできた。例えば、2004年には酸化マグネシウムを絶縁層として用いた世界最高性能のTMR素子の開発に成功している。また、スピントランジスタの基盤技術である磁性体から半導体へのスピン情報入力に関しても、実証実験が行われてきた。

これまで、理論的にはp型ゲルマニウムにおける「スピン緩和時間」(スピン情報が半導体に入力されてから情報を失うまでの時間)が室温では極めて短いと予想され、室温でのスピン入力は困難と考えられてきた。

しかし、産総研の研究で得られた半導体中のスピン緩和時間の実測値は、理論予測よりも遥かに長かったという。よって、産総研の持つ強磁性トンネル電極作製技術をもってすれば、p型ゲルマニウムへの室温での電子スピン入力は十分可能と考えられ、その実証実験に取り組むことにしたのである。

画像1が、電子スピン入力実験に用いた素子の構造だ。p型ゲルマニウム基板とスピン情報源である鉄と厚さ約2ナノメートル(nm)の酸化マグネシウムを積層した電極から構成される。

この素子に垂直方向に電流を流すことにより、鉄からのスピン情報がゲルマニウム中へ入力される仕組みだ。ゲルマニウム中の電子スピン情報の有無は、「ハンル効果」と呼ばれる現象を利用して調べられた。

ハンル効果とは、半導体などの非磁性体中に入力されたスピンの向きが外部から印加された磁界の影響を受けて回転し、電気抵抗などに影響を与える現象のことだ。この効果を調べることにより、半導体へのスピン入力の有無を判断することができるのである。

なお、ハンル効果を観測するために必要なのが、磁性体膜(今回の素子では電極)に対して垂直方向に弱い磁界を印加することだ。これにより、磁性体膜の磁化の向きを変えずに、ゲルマニウム中に入力された電子スピンの向きを変えることができるのである。しかしこの時、電極とゲルマニウム基板間の電圧を減少させるように電子スピンの向きが変化してしまう。

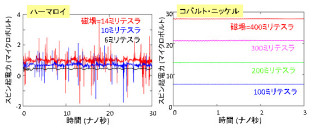

画像3は、室温における素子電圧の外部磁場に対する応答の測定結果だ。発生する電圧は印加磁場に対して減少しているが、これがハンル効果に特有の現象である。

観測された電圧(ハンル信号)から、室温でのp型ゲルマニウム中の「スピン拡散長」を見積もったところ、理論的な予想値より数桁長く、スピントランジスタへの応用に必要な長さ(50nm程度)より十分に長い80nm以上あることが判明した。これは、p型ゲルマニウムを用いたスピントランジスタの実現が十分に可能であることを示している。

スピン拡散長とは、物質中において、電子や正孔がスピン情報を保ったまま伝搬可能な距離の目安を与える長さのこと。スピントランジスタの実現のためには、この長さがトランジスタのソース・ドレイン電極の間隔よりも長いことが必要だ。

次世代半導体材料であるp型ゲルマニウム中へ電子スピン情報を室温で入力できたことは、スピントランジスタの実現に繋がるものであり、将来のグリーンITの発展に大きく貢献できると期待されるという。研究グループは今後、さらに電子スピン入力の高効率化に取り組み、ゲルマニウムを用いたスピントランジスタの実現を目指すとしている。