MathWorksは3月2日(米国時間)、MATLABおよびSimulinkプロダクトファミリの最新版となる「リリース2012a(R2012a)」を発表した。

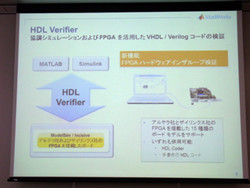

R2012aでは、84の製品アップデートが施され、FPGAやASICでのプロトタイピングや実装のためにMATLAB/SimulinkよりHDLコードを生成する「HDL Coder」やEDA Simulator Linkの後継製品で、新たにAlteraのFPGAのハードウェア・イン・ザ・ループのサポートを追加した「HDL Verifier」が導入された。

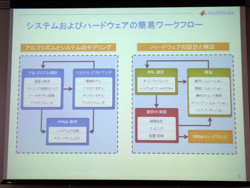

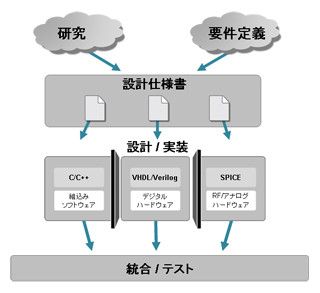

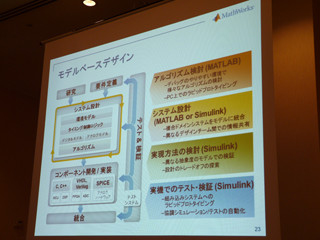

組込機器などの現場では、アルゴリズム開発とハードウェア開発が平行して進められる。具体的にはアルゴリズムを元にハードウェアの制約を考慮してシステムの開発が行われるわけだが、ハードウェアへの実装時などでバグが見つかった場合、それがアルゴリズムに起因しているのか、ハードウェア側の設計ミスなのかの切り分けが難しかった。また、アルゴリズムの複雑化による現実的でないハードウェアスペックの要求なども出てくるようになり、そうした課題の解決が求められていた。しかし、開発現場は往々にしてアルゴリズム開発とハードウェア開発は別々のチーム(会社単位で異なることもある)で行われており、協調設計/開発を実際に進めていくということに対して問題が生じ、その結果、最終製品の仕様変更を悪いほうに行わざるを得なかったり、デバッグ作業に時間がかかり、納期に間に合わせるためにデバッグ不足で出荷ということも起きるなど、課題が山積されているのが現状である。

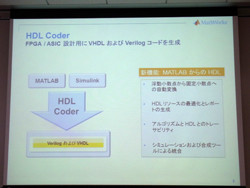

こうしたアルゴリズムの検証とハードウェアの検証作業のスムーズなやりとりの実現を目指したのが今回のHDL Coderで、従来、Simulinkで生成したコードをHDL化するためのツール(Simulink HDL Coder)として存在していたツールを、今回のバージョンよりMATLAB環境からでも、そうした浮動小数点演算から固定小数点演算への自動変換や、HDLリソースの最適化とレポートの作成、アルゴリズムとHDLとのトレーサビリティなどを実行することを可能とした。これにより、VHDLもしくはVerilogコード(任意で選択可能)をMATLAB関数およびSimulinkモデルから生成できるようになり、FPGAのプログラミングやASICのプロトタイピングと設計に用いて、実行および検証を行うことが可能となった。また、Simulinkモデルと生成したHDLコードとの間のトレーサビリティによって、DO-254などの標準規格に準拠する高信頼性アプリケーションの開発もサポートしている。

一方のHDL Verifierは、VHDL/Verilogコードの検証および協調シミュレーションツールで、新たに追加された機能としてFPGAハードウェア・イン・ザ・ループ検証があり、これを用いることで、HDL Coderから吐き出したコードのほか、自分で書いた手書きのHDLコードも検証することができるようになる。また、現時点(3月5日時点)では、XilinxおよびAlteraのFPGAを搭載した15種類のボードモデルで動作確認済みで、今後、そのほかのボードも検証を進め、随時対応ボードのリストを更新していく予定とのことである。

|

|

HDL Verifierを用いることで、MATLAB/Simulinkで生成したVHDL/Verilogコードや、AlteraのQurtusやXilinxのデザインスイートなどで生成したVHDL/Verilogコードの検証が可能となる |

なお、今回のバージョンでHDL関連が大きく強化されたことについて同社では「もともとMATLABコードからHDLコードを生成したいというニーズはあった。従来はSimulinkがないとできなかったが、そのためだけにSimulinkを使いたくないという声が強く、今回の機能強化にいたった」と背景を説明しており、活用を想定するユーザー層としては、開発の上流においてアルゴリズム設計をしているエンジニアで、「MATLABのコードで下流に設計資産を渡すのではなく、HDLで渡すことによりハードウェア開発側のエンジニアにも、よりアルゴリズムを理解してもらえるようにすることができるようになる」と説明している。