産業技術総合研究所(産総研) ナノエレクトロニクス研究部門 強誘電体メモリグループの酒井滋樹 研究グループ長らは、東京大学(東大)大学院 工学系研究科 竹内健 准教授と共同で、強誘電体ゲート電界効果トランジスタ(FeFET)をメモリセルとして用いる強誘電体NAND型フラッシュメモリ(Fe-NANDフラッシュメモリ)の64kビットメモリアレイを開発したことを明らかにした。同成果は、「2011 International Conference on Solid State Devices and Materials(SSDM 2011)」にて発表される。

現在、SSDなどに用いられるNAND型フラッシュメモリはプロセスの微細化に伴い、書き換え可能回数は約1万回程度と、データセンターのサーバなどに用いるには不安が残る寿命となっている。さらに、プロセスの微細化が進めば、メモリセルの寸法も縮小され、書き換え可能回数も減少することが危惧されており、より書き換え耐性が高く、メモリセルの寸法縮小が可能な次世代不揮発性メモリの開発が求められている。

産総研でも様々な不揮発性メモリの研究を行ってきており、FeFETについては、2002年にPt/SrBi2Ta2O9/Hf-Al-O/Siの積層ゲート構造を用いてデータ保持時間を長くすることに成功して以降、自己整合技術による寸法縮小の実証や、Fe-NANDフラッシュメモリセルの開発などを行ってきていた。

今回の研究は、FeFETの集積化技術により全ビット測定が可能な64kビット Fe-NANDフラッシュメモリアレイを作製し、2日間の測定によりブロックレベル(2kビット)で良好なデータ保持特性を実証したというもの。

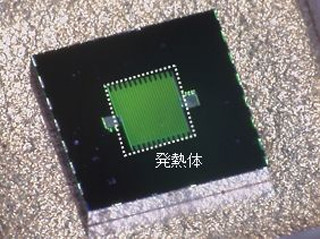

具体的な製造手順は、Fe-NANDフラッシュメモリアレイ回路として働くように設計したSi半導体基板の上に大面積パルスレーザー蒸着法によって高誘電体Hf-Al-O薄膜を約7nm、強誘電体SrBi2Ta2O9(SBT)薄膜を約500nm製膜した後、Ptを約220nm製膜。その後、フォトリソグラフィによりゲート電極とコンタクトホールを形成し、層間絶縁膜を挟んだ2層の金属配線層(M1、M2)を用いて回路を構成したというもの。メモリセルはPt/SBT/Hf-Al-O/Siの金属-強誘電体-絶縁体-半導体ゲート積層構造を持つnチャネル型のFeFETで、ゲート長(L)およびゲート幅(W)はともに5μm。これを縦256×横256の64k個集積してメモリセルアレイを構成した。

64kbメモリセルアレイの2辺に接続したブロック選択回路とビット線選択回路も、nチャネル型およびpチャネル型のFeFETによるCMOS型回路で構成し、こうした選択回路を含めると合計で84k個のFeFETで構成されている。

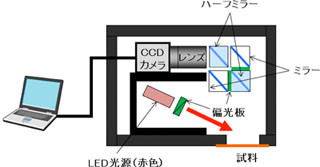

ブロック選択回路により32ブロックのうちの1ブロックを、ビット線選択回路により256本のビット線のうち隣接する2本を、それぞれ選択することができ、今回試作したテストチップでは、ワード線電圧とビット線電圧は外部パッドから与え、読み出しはビット線電流を直接測定して行った。また、パルス発生機器、直流電流・電圧源、半導体パラメータアナライザなどを組み合わせて測定系を構築し、自動計測を行った。

|

|

今回作製された64kビット Fe-NANDフラッシュメモリアレイ。(a)はチップの全体写真、(b)はチップの右下隅を拡大した光学顕微鏡写真、(c)は1ブロック内の回路の概略図、(d)はメモリセルアレイ断面の概略図、(e)はメモリセルアレイ断面の走査型電子顕微鏡写真 |

実際にこの64kビット Fe-NANDフラッシュメモリアレイを用いて、ブロック消去、ページ書き込み、データ非破壊読み出しを行ったところ、すべてのメモリセルにアクセスできることが確認され、全ビット消去と全ビット書き込み、市松模様状書き込みの3通りのパターンを書き込み、および読み出しに成功したという。

また、ブロックレベル(2kビット)で2日間の測定による良好なデータ保持特性のほか、セルレベルでは1億回書き換え可能であることも確認できたとしている。

今回の技術を応用、発展させていくと、将来的には、Fe-NANDフラッシュメモリのデータ書き込み時のビット線電圧は1V、ワード線電圧は6Vまで下げることができ、従来のNAND型フラッシュメモリと比べて消費電力は約7分の1になると見込まれることから、研究チームでは、今後、Fe-NANDフラッシュメモリセルの微細化を進め、シリコンデバイスにおける目安のサイズの1つであるゲート長0.18μmを達成し、その後、さらに小さいゲート長0.05μmでデータセンター向けSSDをターゲットとしたFe-NANDフラッシュメモリの実用化を数年以内に目指すとしている。