CPUとHMCの間のリンクは送受それぞれ16ペアの差動伝送の信号線があり、10Gbit/sの信号伝送を行うので、1本のリンクの送受合計の伝送バンド幅は40GB/sとなる。従って、リンク数が4本のHMCの場合は160GB/s、リンク数8本のHMCの場合は320GB/sのCPU-メモリ間伝送バンド幅が得られる。

更に、このロジックチップはメモリアクセスの順序を最適化したり、DRAMの消費電力を抑えるような制御機能を持っている。更に、高信頼、高可用性機能を備えており、ECCでエラー訂正を行ったり、不良が発生したスライスを修理したりする機能ももっている。また、CPUとのリンクのデータ転送エラーを検出する機能を持ち、エラーが修復不可能な場合はそのリンクだけを切断し、残りのリンクで動作を継続するなどの機能を持っている。

第1世代のHMCは、50nmプロセスで製造された1GbitのDRAMチップ 4枚を積層している。このHMCは電源電圧1.2Vで動作し、メモリバンド幅128GB/sで消費電力は11.08Wである。一方、DDR3-1333モジュールのバンド幅は10.33GB/sで消費電力は5.2Wであるので、電力は2倍強であるがバンド幅は10倍以上であり、計算上のビットあたりの消費エネルギーはDDR3が64.7pJ/bitに対してHMCは10.82pJ/bitと約1/6のエネルギーとなっている。現在のDRAMは30nmを切る微細プロセスを使っているので、それに比べると1~2世代古いプロセスのDRAMを使いながら、HMCは10倍以上のメモリバンド幅を1/6のエネルギーで実現しており、最近のプロセスを使えば、更に性能を向上させられる筈である。

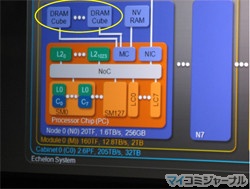

高バンド幅のHMCは、大量のメモリアクセスを必要とするスパコンのメモリとしては最適である。実は、米国のDARPA(国防高等研究計画局)の推進するExtremeScale UHPCシステムを開発するプロジェクトを受注したNVIDIAのEchelonチームにはMicronが入っており、2010年11月のSC2010でNVIDIAのチーフサイエンティストのBill Dally氏のEchelon計画のプレゼンテーションにはシステムのメモリとしてDRAM Cubeが描かれている。

|

|

|

ExtremeScale UHPCプロジェクトのNVIDIAを中心とするEchelonチームのメンバにはMicronが入っている |

SC 10で発表されたNVIDIAのシステムイメージの図にはDRAM Cubeが入っている |

TSVは、新たな付加価値を生む技術ということで半導体各社が実用化を急いでいるが、ビアを掘る深さと直径には制約があり、深い穴は直径も大きくなってしまう。このため、DRAMウェハの裏を削って薄くしてからTSVを作る。しかし、それでもTSVの直径は数ミクロン程度で、それが多数あるとDRAMに使えるチップ面積が減ってしまう。また、ウェハを薄くする研磨やTSVの形成、HMCを構成するためのチップの接続などの追加の工程が必要であり、製造コストが高くなる。更に、研磨以降の工程で不良が出ると、そのロスもコストアップになってしまう。 ということで、HMCがメモリバンド幅を大きく改善し、ランダムアクセス性能や信頼性を改善することは確かであるが、これらの改善に見合う値段で何時ごろ提供できるようになるかは、まだ、未知数である。

しかし、DARPAのExtremeScale UHPCプロジェクトの予算を使って行われるMicronのHMCの開発がDRAMメモリ高性能化の1つのフロンティアを推し進めることは間違いない。