Lattice Semiconductorは、自社の「Lattice Platform Manager」、「Powermanager II」および「ispClock」デバイスをサポートミクスドシグナル設計ソフトウェアの新バージョン「Lattice PAC-Designer 6.1」をリリースした。また、併せて自社FPGAのデザイン環境向けフラッグシップ製品「Lattice Diamond デザインソフトウェア 1.3」もリリースしたことを発表した。

これらは、統合された状態で利用することが可能であり、これによりPlatform Managerを使用する設計者は自動化されたシミュレーション環境を活用することができるようになり、従来以上に高度なデジタル設計を実現することが可能となる。

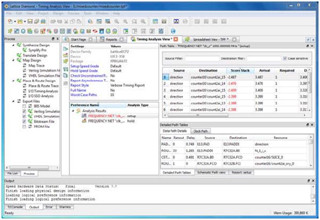

例えば、内部CPLDにより制御されるアナログI/Oピン機能をテストしたり、あるいはFPGA制御セクション内のVerilogまたはVHDLで記述された拡張デジタル制御機能の統合を確認するなど、デザイン全体をコンパイルして必要なスティミュラス・ファイルのテンプレートを作成し、AldecのActive-HDL Simulator内で初期タイミング波形を自動的に生成することが可能となった。従来、こうした作業は手作業で行っていたが、PAC-Designer 6.1では最適化・自動化がなされているため、マウスをクリックするだけで、必要なすべてのデザインファイルと初期のタイミング・フローチャートを生成することが可能となった。

また、PAC-Designer 6.1には、Platform Manager開発キットを対象とした4つの参照デザインとして、障害ログおよび監視、拡張閉ループトリム、長時間遅延タイマ、およびADC電圧測定などが含まれているほか、PWMファン制御、I2Cスレーブ-SPIマスタブリッジ接続およびBSCAN1マルチスキャンポート・アドレス可能バッファなどの11の参照デザインが同社Webサイトより入手することが可能となっている。

一方のDiamond 1.3は、MachXO2ファミリへの対応も強化しており、最終製品のSSOモデルや、LCMX02-1200およびLCMX02-1200Uデバイス向けのビットストリームを提供するほか、大容量かつコスト条件の厳しいアプリケーションが必要とするLCMXO2-2000Uのウェハ・レベル・パッケージのサポートも追加している。さらに、論理合成とMAPおよびPAR実装エンジンの継続的な改善との相乗効果により、LCMXO2デバイスをターゲットとするほとんどの設計において、最大動作周波数(Fmax)が、5%から15%程度向上することが可能となっている。

なお、いずれのソフトウェアはともに同社のWebサイトよりダウンロードして利用することが可能。一度ダウンロードしてインストールしたソフトウェアは、Lattice Diamond無償版ライセンス、またはLattice Diamond有償版(Subscription)ライセンスのいずれかで使用できる。無償版ライセンスは、同社のWebサイトからの申し込みを受けてすぐに発行され、MachXO2およびMachXOファミリ、LatticeXP2ファミリおよびLatticeECP2ファミリなどの同社FPGAデバイスに無償でアクセスできるようになる。また無償版ライセンスでは、同社論理合成ツールのほか、AldecのLattice Edition II混在言語シミュレータ、SynopsysのSynplify Pro for Lattice論理合成ツールを利用することができる。さらに、Lattice Diamond有償版ライセンスでは、Lattice ECP3を含む同社のすべてのFPGAがサポートされており、ライセンス価格は1年間で895ドルとなっている。