富士通研究所は2月2日、内部電極に銅を使用した高速LSI用キャパシタのプロセス技術を開発したことを発表した。銅を内部電極に用いることでキャパシタ自身のインピーダンスを低くできるほか、キャパシタをLSIの直下に搭載することで配線によるインピーダンスも低減でき、電流供給効率が従来に比べ10倍向上したという。

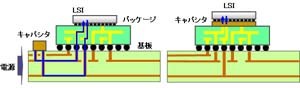

近年、LSIの高速化、高集積化が進み、多くの素子が同時に動作する際に、素子の周辺で一度に多くの電流が消費されるようになってきた。この時、LSIの電源電圧は降下しやすく、正常な動作に影響を与えることがあり、こうした多くの電流が消費される際には、即座に電流を補う必要があるため、LSIの近くにキャパシタを設置することが望まれており、従来は、電源供給キャパシタとしてセラミックチップコンデンサをLSIパッケージおよび基板の表面や裏面に搭載し、配線を介してLSIへ電流供給を行っていた。

しかし、この方法では、キャパシタからLSIまでの接続配線が長いためにインピーダンスが大きく、将来の高速コンピュータではLSIの高速動作が不安定になる可能性があるという課題があった。また、キャパシタ部品の内部電極に抵抗値の比較的大きなニッケルなどを使用しているためにキャパシタ自身のインピーダンスも大きく、電源電流の高速供給に限界があった。

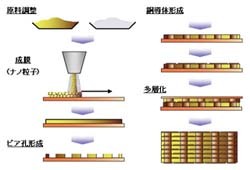

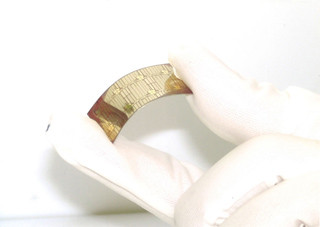

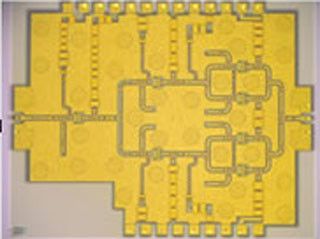

今回、富士通研究所では、こうした課題に対応し、高速LSIに電流を迅速に安定して供給するためのキャパシタの基本的なプロセス技術としてナノサイズのセラミック粒子を用いて無機材料の膜を形成する「ナノ粒子成膜技術」を開発。同技術ではLSIの直下に接続が可能な微細な貫通電極構造を採用し、電気抵抗の低い銅の内部電極への適用が可能となったほか、高容量化(1μF/cm2・層)が可能で信頼性が高い薄膜の誘電体層を有するキャパシタを作製することが可能になった。

銅を内部電極とすることで、キャパシタ自身のインピーダンスを低くすることが可能になり、キャパシタ・LSI間の配線長が短くなることから、電源供給ラインのインピーダンスを抑えることができるようになり、結果として高速LSIの動作安定化に向けた電流供給効率が10倍以上向上し、コンピュータの高速化が可能となるという。

なお、今後、富士通研究所では、キャパシタの端子の微細化と多層化技術の開発をさらに進め、2015年頃にコンピュータへの適用を目指すとしている。