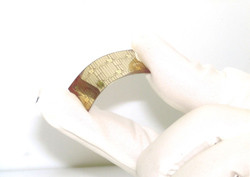

富士通研究所は、ZnO系の半導体を用いて銅やガラス、プラスチックなど、平面状の物質なら何にでも電源トランジスタの作製が可能な技術を開発したことを明らかにした。

低損失の電源トランジスタを実現可能なワイドバンドギャップ半導体であるZnO系は、どこにでもトランジスタを形成することが可能な材料で、LCDのITO代替などの研究開発が進められている。

しかし、ZnO系で高電圧電源トランジスタを作製するためには、高耐圧を実現する上で必要となるチャネル材料の低濃度化が難しい点や、電界集中の原因となる材料表面に存在する電荷トラップ抑制などの課題があった。

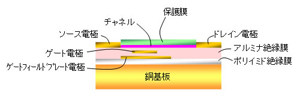

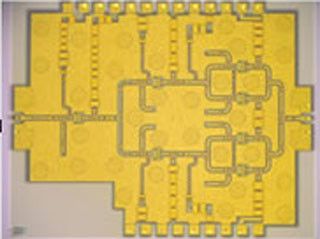

今回、富士通研では、材料としてインジウムガリウム酸化亜鉛(IGZO)を用い、電源トランジスタのチャネル部分をポリマー被膜で保護することで、電源用の100V電圧でのトランジスタ動作に成功した。

また同技術は、高耐圧トランジスタをパッケージ材料である銅基板上に直接作製できるため、放熱性の確保が容易となるほか、コストの低減も可能となる。

これにより同技術を活用することで、あらゆる平面状の物質への電源回路の作製が可能になるほか、高電圧を発生するようなセンサや圧電素子などへ応用することも可能となる。

なお、富士通研では今後、電源トランジスタとして要求される高耐圧化と、オン抵抗の低減を進め、2015年頃にIT機器への搭載を目指すとしている。