米国の国防総省の先端研究開発を担当するDARPA(Defense Advanced Research Project Agency)が、2010年8月にExtreme-Scale Computing Projectの開始を発表した。2018年に50GFlops/W以上の電力効率を持ち、1筐体で1PFlops以上の処理能力という目標で、この技術ができればExaFlopsのスパコンシステムを作ることができるようになるという技術を開発する。

2018年までの前半の4年間がPhase-1、後半の4年間がPhase-2である。このPhase-1の契約を獲得したのは、それぞれNVIDIA、Intel、MIT、Sandia国立研究所をリーダーとする4つのチームである。なお、DARPAのプロジェクトではPhase-1の成果を審査して、Phase-2では1~2チームに絞り込むのが普通であり、ハードの開発という点ではNVIDIAとIntelの一騎打ちということになる。

NVIDIAのプロジェクトはEchelonと名付けられており、チームにはCRAY、Micron Technology、Lockheed Martin、オークリッジ国立研究所、ユタ大学、ペンシルバニア大学、テキサス大学オースティン校、テネシー大学、ジョージア工科大学が加わっている。

SC10において、NVIDIAのBill Dallyチーフサイエンティストが基調講演を行い、その中でこのEchelonプロジェクトの計画を公表した。

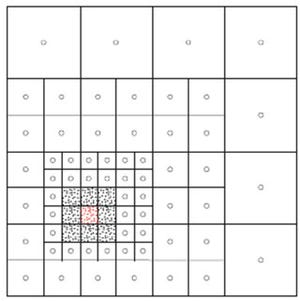

図2の拡大図を見ると、NoC(Network on Chip)の下側にはSM0~SM127と128個のStreaming Multiprocessorが並んでいる。そして、各SMにはC0~C7の8個のコアがあり、それぞれのコアにはL0キャッシュがついている。さらにSM群の右側にはLC0~LC7というユニットがあるが、これはシングルスレッド性能の高い汎用CPUコアである。そして、NoCの上側には1024個のL2キャッシュとMC(Memory Controller)、NIC(Network Interface Controller)が配置されている。

現在のGPUを使用したシステムでは、PCI Expressを通してIntelなどの汎用CPUにGPUを付けるという形態になっているが、Echelonでは、GPUとCPUを1つのプロセサチップに内蔵しNoCを介してSM群とL2キャッシュを共用する構成となっている。

そして、MCの先にはDRAM Cubeが接続されている。DRAM Cubeがどのようなものであるかは明らかではないが、名前から想像するに、3次元実装されたDRAMと思われる。後に述べるように、DRAMとのデータのやり取りに必要なエネルギー消費は大きいので、できるだけ配線を短くしてこのエネルギー消費を押さえようという意図と思われる。

図1に示すように、このプロセサチップを8個まとめたものがモジュールであり、16個のモジュールを1つの筐体(キャビネット)に収容することになっている。

各プロセサチップのピーク演算性能は20TFlops、 メモリバンド幅は1.6TB/s、そしてDRAM Cubeの総メモリ容量は256GBである。また、この図には描かれていないが、NICのバンド幅は150GB/sである。NVIDIAの、現在のTesla M2070 GPUボードはピーク演算性能が0.515TFlops、ピークメモリバンド幅が150GB/s、メモリ容量が6GBであるのと比較すると、Echelonチップの目標はピーク演算性能で約40倍、メモリバンド幅で約10倍、メモリ容量で約40倍ということになる。

NVIDIAのロードマップは世代ごとに3~4倍の性能向上を行うというもので、2011年投入のKeplerはFermiの3~4倍、2013年に投入するMaxwellはFermiの前世代の40倍(Fermiの10倍程度)と発表している。このEchelonはMaxwellの4倍の性能であり、Maxwellの次世代という位置づけになると考えられる。

そして1筐体に収容される128個のプロセサチップのNICからのインタコネクトはHigh Radix Router Moduleに接続されている。High Radix Routerの技術はDally氏がStanford大学の教授の時(StanfordのWebサイトによると、Dally氏は今も教授の職にあるが、給与はStanford大以外のところから支払われているというステータスである)に開発した技術で、CRAYのXE6スパコンで使用されており、この発展系が使われるのであろう。さらに、筐体間は光ファイバを使うDragonfly Interconnectで接続されている。このDragonfly InterconnectもDally氏の発明によるインタコネクト技術である。

これで1筐体のピークFlopsは2.6PFlopsとなり、Extreme-Scale Computingの目標をクリアすることができる。

しかし、問題は消費電力である。