日立製作所は9月13日、10~30GHzの周波数帯域を利用する準ミリ波帯無線通信システム向けに、低コストなSi系半導体を用いた高周波送受信回路技術を開発、消費電力を従来の3分の1となる100mWで動作する24GHz帯の1チップMMIC(Monolithic Microwave Integrated Circuit)を試作したことを発表した。

同回路技術は、従来、使用されてきた化合物半導体に比べて低コストなSi系半導体を用い、また複数のICチップで構成されていたものを1つのICチップで回路を構成することで、低コスト化と小型化を実現したというもの。また、送受信回路の各機能を司る要素回路を接続している結合回路に、電力供給を必要としない受動素子を用いることで、消費電力の低減を実現した。

従来、この結合回路には能動素子が用いられてきたが、動作周波数が準ミリ波帯まで高くなると、要素回路と結合回路の間で電気整合がとりにくくなる問題(インピーダンス不整合)が発生して信号伝達の効率を劣化させるため、これを補う大きな動作電流が必要となり、消費電力の増加が生じていた。

今回、開発された結合回路は、渦巻き形状に作成した結合素子を利用することで要素回路と結合回路のインピーダンス不整合を解消、信号伝達効率の向上を実現しているほか、信号伝達に交流信号だけを利用することから、直流信号も含めて伝達している従来の能動素子を用いた結合回路に比べて電源電圧を低減することが可能となっている。

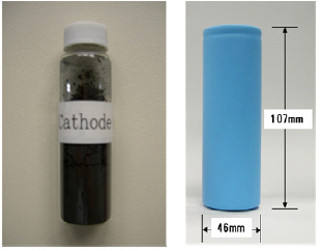

同社では、開発した高周波送受信回路技術の有効性を実証するために、0.18µm SiGe BiCMOSプロセスを用いて、24GHz帯1チップ送受信回路を試作、従来の3分の1となる100mWの消費電力で、最大利得60dB、雑音指数5.8dBの受信回路特性を、また利得38dB、送信線形出力4.3dBmの送信回路特性を実現することを確認したという。

なお、同技術の詳細は、9月13日よりスペインにて開催される「欧州固体素子回路会議(ESSCIRC:European Solid-State Circuits Conference)」にて、9月14日(現地時間)に発表される予定。